# COMPUTER ORGANIZATION

**MCA 105**

**SELF LEARNING MATERIAL**

# DIRECTORATE OF DISTANCE EDUCATION

SWAMI VIVEKANAND SUBHARTI UNIVERSITY

MEERUT – 250 005,

UTTAR PRADESH (INDIA)

| SLM Module Developed By :                                                                                                                                                                                |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Author:                                                                                                                                                                                                  |

| Reviewed by :                                                                                                                                                                                            |

| Assessed by:                                                                                                                                                                                             |

| Study Material Assessment Committee, as per the SVSU ordinance No. VI (2)                                                                                                                                |

|                                                                                                                                                                                                          |

| Copyright © Gayatri Sales                                                                                                                                                                                |

|                                                                                                                                                                                                          |

| <u>DISCLAIMER</u>                                                                                                                                                                                        |

| No part of this publication which is material protected by this copyright notice may be reproduced                                                                                                       |

| or transmitted or utilized or stored in any form or by any means now known or hereinafter invented, electronic, digital or mechanical, including photocopying, scanning, recording or by any information |

| storage or retrieval system, without prior permission from the publisher.                                                                                                                                |

|                                                                                                                                                                                                          |

| Information contained in this book has been published by Directorate of Distance Education and has                                                                                                       |

| been obtained by its authors from sources be lived to be reliable and are correct to the best of their                                                                                                   |

| knowledge. However, the publisher and its author shall in no event be liable for any errors, omissions or damages arising out of use of this information and specially disclaim and implied              |

| warranties or merchantability or fitness for any particular use.                                                                                                                                         |

|                                                                                                                                                                                                          |

|                                                                                                                                                                                                          |

|                                                                                                                                                                                                          |

| Published by: Gayatri Sales                                                                                                                                                                              |

**Printed at:** Gayatri Sales, Meerut.

**Typeset at**: Micron Computers

# **COMPUTER ORGANIZATION (MCA – 105)**

# **Unit-I** (Representation of Information and Basic Building Blocks)

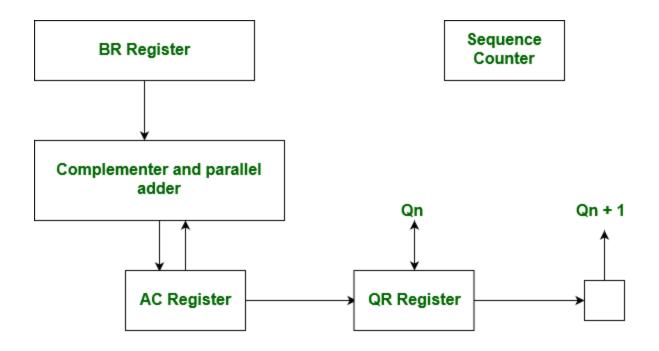

Introduction to Computer, Computer hardware generation, Number System: Binary, Octal, Hexadecimal, Character Codes (BCD, ASCII, EBCDIC), Logic gates, Boolean Algebra, K-map simplification, Half Adder, Full Adder, Subtractor, Decoder, Encoders, Multiplexer, Demultiplexer, Carry lookahead adder, Combinational logic Design, Flip-Flops, Registers, Counters (synchronous & asynchronous), ALU, Micro-Operation. ALUchip, Faster Algorithm and Implementation (multiplication & Division)

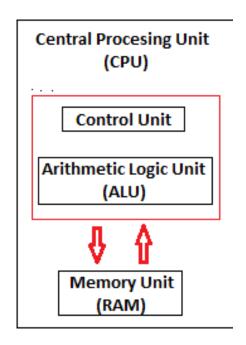

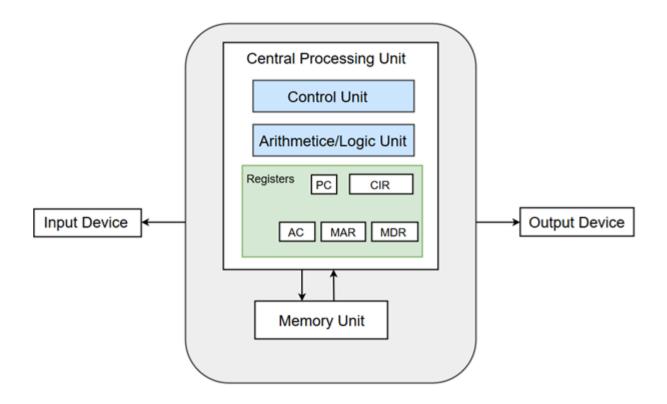

# **Unit-II (Basic Organization)**

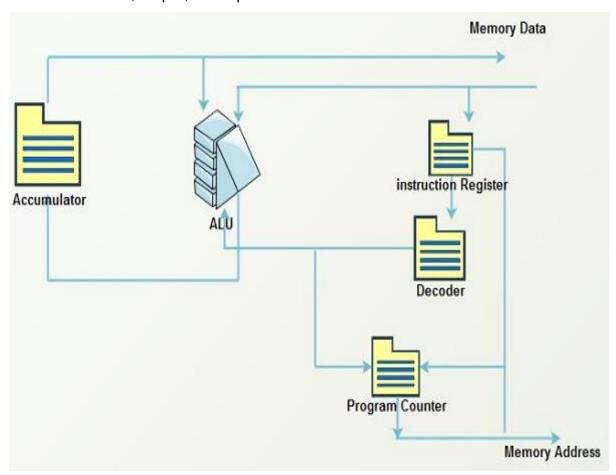

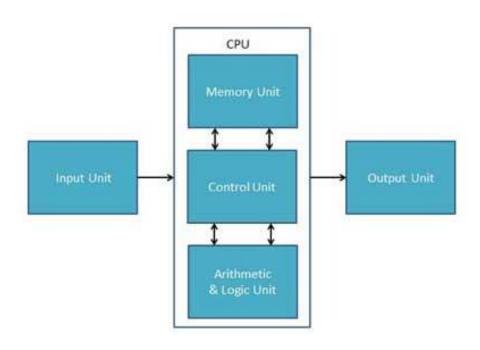

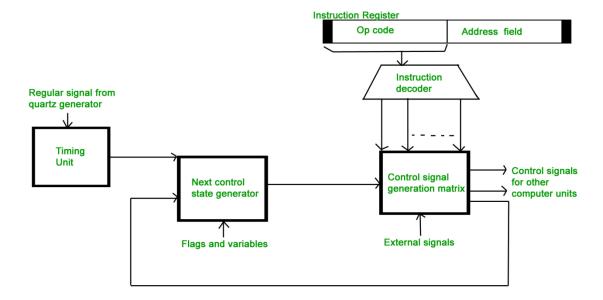

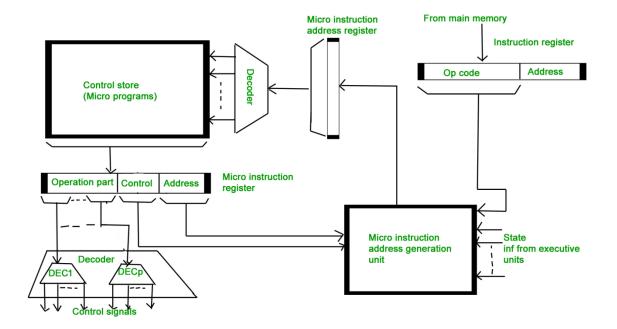

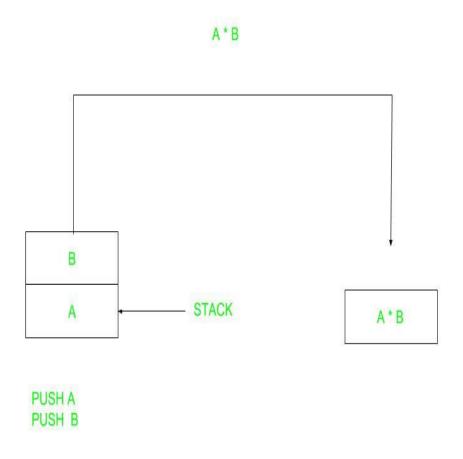

Von Neumann Machine (IAS Computer), Operational flow chart (Fetch, Execute), Instruction Cycle, Organization of Central Processing Unit, Hardwired & micro programmed control unit, Single Organization, General Register Organization, Stack Organization, Addressing modes, Instruction formats, data transfer & Manipulation, I/O Organization, Bus Architecture, Programming Registers

# **Unit-III (Memory Organization)**

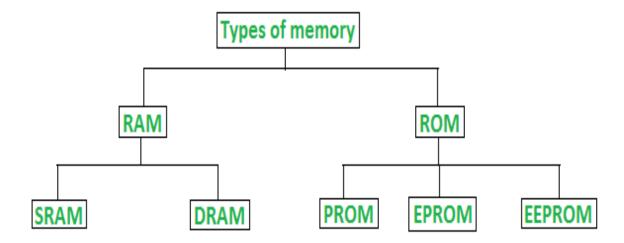

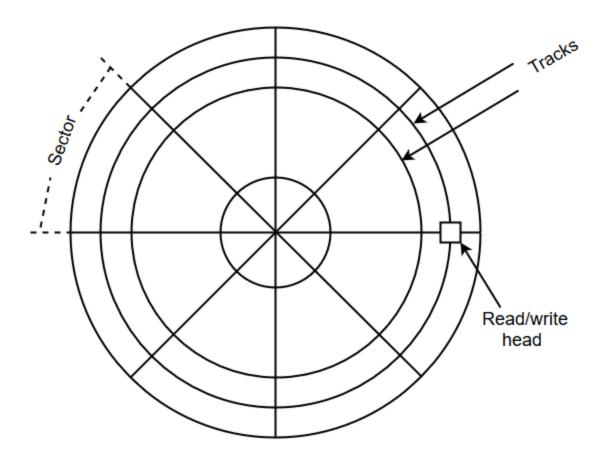

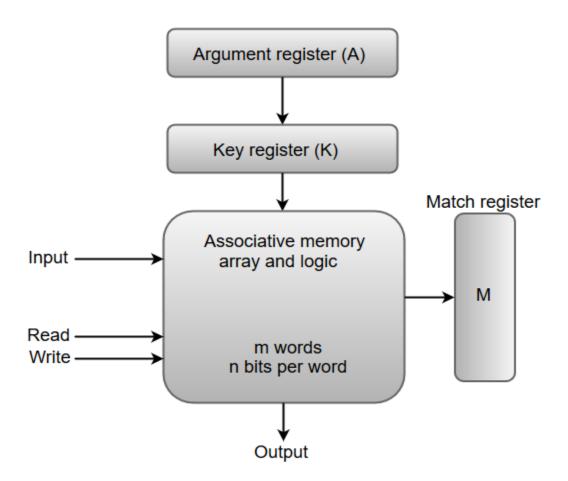

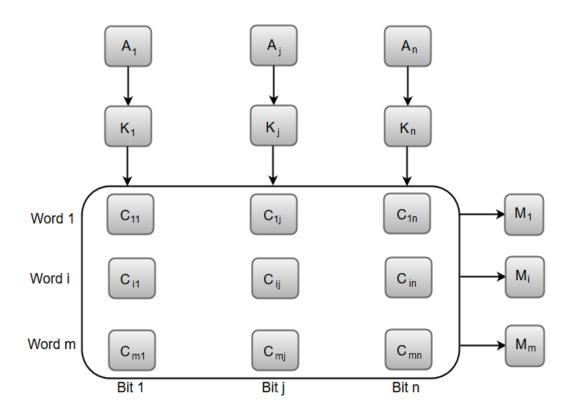

Memory Hierarchy, Main memory (RAM/ROM chips), Auxiliary memory, Associative memory, Cache memory, Virtual Memory, Memory Management Hardware, hit/miss ratio, magnetic disk and its performance, magnetic Tape etc.

# **Unit-IV (I/O Organization)**

Peripheral devices, I/O interface, Modes of Transfer, Priority Interrupt, Direct Memory Access, Input-Output Processor, and Serial Communication. I/O Controllers, Asynchronous data transfer, Strobe Control, Handshaking.

# **Unit-V (Process Organization)**

Basic Concept of 8-bit micro Processor (8085) and 16-bit Micro Processor (8086), Assembly Instruction Set, Assembly language program of (8085): Addition of two numbers, Subtraction, Block Transfer, find greatest number, Table search, Numeric Manipulation, Introductory Concept of pipeline, Flynn's and Feng's Classification, Parallel Architectural classification.

# **Unit-I**

# (Representation of Information and Basic Building Blocks) :-

# **Introduction to Computer**

The Bachelor of Computer Applications (BCA) and the Master of Computer Application (MCA) are undergraduate and postgraduate programs or courses which have guidelines and eligibility set out by the All India Council of Technical Education (AICTE). They are typically three-year programs that span six semesters. They are designed to bridge the gap between the studies of computers and its applications. The master's program aims to shape computer professionals with the right moral and ethical values and can prepare students to face the challenges and opportunities in the IT industry of India by building strong foundations.

The syllabus focuses on the core fundamentals of computer science, but generally undergoes revision according to the industry requirement with the aim of increasing employment opportunities for students. Admission to both the BCA and MCA can be obtained by clearing the appropriate entrance exams. Having a background in science can help in grasping concepts, and mathematics is a compulsory subject. BCA and MCA graduates can seek job opportunities in fields like software development, web design, systems management, quality assurance and software testing. A MCA or BCA graduate can work in IT companies big and small in various roles.

#### Various topics covered under BCA and MCA

# **Bachelor of Computer Applications (BCA)**

The Bachelor of Computer Applications course usually consists of core courses in programming with C, algorithm and data structures, advanced programming with C, computer organization and network fundamentals, relational database management systems, Web programming, software engineering and visual programming. Some of the main course highlights are meant to heighten technological know-how, to train students to become industry specialists, to provide research-based training and to encourage software development. The syllabus is intended to not only teach students theory and applications, but can also help equip them with professional and communication skills.

A few of the topics covered under BCA courses are listed below. Each semester has 6 topics to cover so a total of 36 topics are covered in the entire duration of the course. Each semester has Computer Laboratory and Practical work based on the syllabus of that particular semester.

- Business Communication

- Principles of Management

- Programming Principles and Algorithms

- Computer Fundamental and Office Automation

- Business Accounting

- Organizational Behaviour

- Elements of Statistics

- C Programming

- Cost Accounting

- Software Engineering

- C++, Core Java, Advanced Java

# **Master of Computer Applications (MCA)**

In Master of Computer Applications course, higher level subjects like computer organization, data and file structuring using C, operating system, computer networks, modelling and simulation, visual basic, combinatory and graph theory, computer graphics, system programming and computer based numerical and statistical techniques are generally taught. In the final semester, you will most likely need to specialize in a topic in the form of project work. The course stresses the application of theory and computing principles through project work, case studies, presentations and practical assignments. Some of the popular fields which are generally chosen by students for MCA specialization are application software, hardware technology, systems management, systems development, and management information systems.

A few of the topics covered under MCA courses are listed below. Each semester has 6 theoretical topics to cover so a total of 30 topics are covered in the first five semesters of the MCA course. In the sixth and final semester a student has to submit an industrial project. Each semester has a lot of practical work involved based on the syllabus of MCA.

- Accounting and Financial Management

- UNIX and Shell Programming

- Object Oriented Systems in C++

- Design and Analysis of Algorithm

- Modelling and Simulation

- Software Engineering

- Net Framework and C Lab

- WEB Technology

# **Computer hardware generation**

#### Introduction:

A computer is an electronic device that manipulates information or data. It has the ability to store, retrieve, and process data.

Nowadays, a computer can be used to type documents, send email, play games, and browse the Web. It can also be used to edit or create spreadsheets, presentations, and even videos. But the evolution of this complex system started around 1940 with the first Generation of Computer and evolving ever since.

There are five generations of computers.

#### 1. FIRST GENERATION

- Introduction:

- 1. 1946-1959 is the period of first generation computer.

- 2. J.P.Eckert and J.W.Mauchy invented the first successful electronic computer called ENIAC, ENIAC stands for "Electronic Numeric Integrated And Calculator".

## • Few Examples are:

- 1. ENIAC

- 2. EDVAC

- 3. UNIVAC

- 4. IBM-701

- 5. IBM-650

. . .

# Advantages:

- 1. It made use of vacuum tubes which are the only electronic component available during those days.

- 2. These computers could calculate in milliseconds.

# Disadvantages:

- 1. These were very big in size, weight was about 30 tones.

- 2. These computers were based on vacuum tubes.

- 3. These computers were very costly.

- 4. It could store only a small amount of information due to the presence of magnetic drums.

- 5. As the invention of first generation computers involves vacuum tubes, so another disadvantage of these computers was, vacuum tubes require a large cooling system.

- 6. Very less work efficiency.

- 7. Limited programming capabilities and punch cards were used to take inputs.

- 8. Large amount of energy consumption.

- 9. Not reliable and constant maintenance is required.

### 2. SECOND GENERATION

#### Introduction:

- 1. 1959-1965 is the period of second-generation computer.

- 2. 3.Second generation computers were based on Transistor instead of vacuum tubes.

## Few Examples are:

- 1. Honeywell 400

- 2. IBM 7094

- 3. CDC 1604

- 4. CDC 3600

- 5. UNIVAC 1108

#### ... many more

## Advantages:

- 1. Due to the presence of transistors instead of vacuum tubes, the size of electron component decreased. This resulted in reducing the size of a computer as compared to first generation computers.

- 2. Less energy and not produce as much heat as the first genration.

- 3. Assembly language and punch cards were used for input.

- 4. Low cost than first generation computers.

- 5. Better speed, calculate data in microseconds.

- 6. Better portability as compared to first generation

# Disadvantages:

- 1. A cooling system was required.

- 2. Constant maintenance was required.

- 3. Only used for specific purposes.

### 3. THIRD GENERATION

#### Introduction:

- 1. 1965-1971 is the period of third generation computer.

- 2. These computers were based on Integrated circuits.

- 3. IC was invented by Robert Noyce and Jack Kilby In 1958-1959.

- 4. IC was a single component containing number of transistors.

# Few Examples are:

1. PDP-8

- 2. PDP-11

- 3. ICL 2900

- 4. IBM 360

- 5. IBM 370

... and many more

# Advantages:

- 1. These computers were cheaper as compared to second-generation computers.

- 2. They were fast and reliable.

- 3. Use of IC in the computer provides the small size of the computer.

- 4. IC not only reduce the size of the computer but it also improves the performance of the computer as compared to previous computers.

- 5. This generation of computers has big storage capacity.

- 6. Instead of punch cards, mouse and keyboard are used for input.

- 7. They used an operating system for better resource management and used the concept of time-sharing and multiple programming.

- 8. These computers reduce the computational time from microseconds to nanoseconds.

# Disadvantages:

- 1. IC chips are difficult to maintain.

- 2. The highly sophisticated technology required for the manufacturing of IC chips.

- 3. Air conditioning is required.

#### 4. FOURTH GENERATION

#### Introduction:

- 1. 1971-1980 is the period of fourth generation computer.

- 2. This technology is based on Microprocessor.

- 3. A microprocessor is used in a computer for any logical and arithmetic function to be performed in any program.

- 4. Graphics User Interface (GUI) technology was exploited to offer more comfort to users.

# • Few Examples are:

- 1. IBM 4341

- 2. DEC 10

- 3. STAR 1000

- 4. PUP 11

- ... and many more

## Advantages:

- 1. Fastest in computation and size get reduced as compared to the previous generation of computer.

- 2. Heat generated is negligible.

- 3. Small in size as compared to previous generation computers.

- 4. Less maintenance is required.

- 5. All types of high-level language can be used in this type of computers.

## Disadvantages:

- 1. The Microprocessor design and fabrication are very complex.

- 2. Air conditioning is required in many cases due to the presence of ICs.

- 3. Advance technology is required to make the ICs.

#### 5. FIFTH GENERATION

#### Introduction:

- 1. The period of the fifth generation in 1980-onwards.

- 2. This generation is based on artificial intelligence.

- 3. The aim of the fifth generation is to make a device which could respond to natural language input and are capable of learning and self-organization.

- 4. This generation is based on ULSI(Ultra Large Scale Integration) technology resulting in the production of microprocessor chips having ten million electronic component.

# • Few Examples are:

- 1. Desktop

- 2. Laptop

- 3. NoteBook

- 4. UltraBook

- 5. Chromebook

- ... and many more

# Advantages:

- 1. It is more reliable and works faster.

- 2. It is available in different sizes and unique features.

- 3. It provides computers with more user-friendly interfaces with multimedia features.

# Disadvantages:

- 1. They need very low-level languages.

- 2. They may make the human brains dull and doomed.

# **Number System:**

# **Binary**

A binary number system is one of the four types of number system. In computer applications, where binary numbers are represented by only two symbols or digits, i.e. 0 (zero) and 1(one). The binary numbers here are expressed in the base-2 numeral system. For example, (101)<sub>2</sub> is a binary number. Each digit in this system is said to be a bit. Learn about the number system here.

#### able of Contents:

- Definition

- Table

- How to Calculate Binary Numbers

- Positions

- Binary Arithmetic Operations

- Binary Addition

- Binary Subtraction

- Binary Multiplication

- Binary Divison

Uses

Examples

**FAQs**

Number System is a way to represent the numbers in the computer architecture. There are four different types of the number system, such as:

- 1. Binary number system (base 2)

- 2. Octal number system (base 8)

- 3. Decimal number system(base 10)

- Hexadecimal number system (base 16).

In this article, let us discuss what is a binary number system, conversion from one system to other systems, table, positions, binary operations such as addition, subtraction, multiplication, and division, uses and solved examples in detail.

## What is a Binary Number System?

Binary Number System: According to digital electronics and mathematics, a binary number is defined as a number that is expressed in the binary system or base 2

numeral system. It describes numeric values by two separate symbols; 1 (one) and 0 (zero). The base-2 system is the positional notation with 2 as a radix.

The binary system is applied internally by almost all latest computers and computerbased devices because of its direct implementation in electronic circuits using logic gates. Every digit is referred to as a bit.

# What is Bit in Binary Number?

A single binary digit is called a "Bit". A binary number consists of several bits. Examples are:

- 10101 is a five-bit binary number

- 101 is a three-bit binary number

- 100001 is a six-bit binary number

#### **Facts to Remember:**

- Binary numbers are made up of only 0's and 1's.

- A binary number is represented with a base-2

- A bit is a single binary digit.

## Binary Numbers Table

Some of the binary notations of lists of decimal numbers from 1 to 30, are mentioned in the below list.

| Number | Binary Number | Number | Binary Number | Number | Binary Number |

|--------|---------------|--------|---------------|--------|---------------|

| 1      | 1             | 11     | 1011          | 21     | 10101         |

| 2      | 10            | 12     | 1100          | 22     | 10110         |

| 3      | 11            | 13     | 1101          | 23     | 10111         |

| 4      | 100           | 14     | 1110          | 24     | 11000         |

| 5      | 101           | 15     | 1111          | 25     | 11001         |

| 6      | 110           | 16     | 10000         | 26     | 11010         |

| 7  | 111  | 17 | 10001 | 27 | 11011 |

|----|------|----|-------|----|-------|

| 8  | 1000 | 18 | 10010 | 28 | 11100 |

| 9  | 1001 | 19 | 10011 | 29 | 11101 |

| 10 | 1010 | 20 | 10100 | 30 | 11110 |

# How to Calculate Binary Numbers

For example, the number to be operated is 1235.

| Thousands | Hundreds | Tens | Ones |

|-----------|----------|------|------|

| 1         | 2        | 3    | 5    |

This indicates,

$$1235 = 1 \times 1000 + 2 \times 100 + 3 \times 10 + 5 \times 1$$

Given,

| 1000 | $= 10^3 = 10 \times 10 \times 10$                         |

|------|-----------------------------------------------------------|

| 100  | $= 10^2 = 10 \times 10$                                   |

| 10   | $= 10^1 = 10$                                             |

| 1    | = 10 <sup>0</sup> (any value to the exponent zero is one) |

The above table can be described as,

| Thousands       | Hundreds        | Tens            | Ones            |

|-----------------|-----------------|-----------------|-----------------|

| 10 <sup>3</sup> | 10 <sup>2</sup> | 10 <sup>1</sup> | 10 <sup>0</sup> |

| 1               | 2               | 3               | 5               |

Hence,

$$1235 = 1 \times 1000 + 2 \times 100 + 3 \times 10 + 5 \times 1$$

$$= 1 \times 10^{3} + 2 \times 10^{2} + 3 \times 10^{1} + 5 \times 10^{0}$$

The decimal number system operates in base 10, wherein the digits 0-9 represent numbers. In binary system operates in base 2 and the digits 0-1 represent numbers, and the base is known as **radix**. Put differently, and the above table can also be shown in the following manner.

| Thousands | Hundreds        | Tens            | Ones            |                       |

|-----------|-----------------|-----------------|-----------------|-----------------------|

| Decimal   | 10 <sup>3</sup> | 10 <sup>2</sup> | 10 <sup>1</sup> | 10 <sup>0</sup>       |

| Binary    | 2 <sup>3</sup>  | 2 <sup>2</sup>  | 2 <sup>1</sup>  | <b>2</b> <sup>0</sup> |

We place the digits in columns 10<sup>0</sup>, 10<sup>1</sup> and so on in base 10. When there is a need to put a value higher than 9 in the form of 10<sup>(n+1)</sup> for instance, to add 10 to column 10<sup>0</sup>, you need to add 1 to the column 10<sup>1</sup>.

We place the digits in columns  $2^0$ ,  $2^1$  and so on in base 2. To place a value that is higher than 1 in  $2^n$ , you need to add  $2^{(n+1)}$ . For instance, to add 3 to column  $2^0$ , you need to add 1 to column  $2^1$ .

# **Position in Binary Number System**

In the Binary system, we have ones, twos, fours etc...

For example 1011.110

It is shown like this:

$$1 \times 8 + 0 \times 4 + 1 \times 2 + 1 + 1 \times \frac{1}{2} + 1 \times \frac{1}{4} + 0 \times \frac{1}{8}$$

= 11.75 in Decimal

To show the values greater than or less than one, the numbers can be placed to the left or right of the point.

For 10.1, 10 is a whole number on the left side of the decimal, and as we move more left, the number place gets bigger (Twice).

The first digit on the right is always Halves ½ and as we move more right, the number gets smaller (half as big).

In the example given above:

- "10" shows '2' in decimal.

- ".1" shows 'half'.

- So, "10.1" in binary is 2.5 in decimal.

## **Binary Arithmetic Operations**

Like we perform the arithmetic operations in numerals, in the same way, we can perform addition, subtraction, multiplication and division operations on Binary numbers. Let us learn them one by one.

# **Binary Addition**

Adding two binary numbers will give us a binary number itself. It is the simplest method. Addition of two single-digit binary number is given in the table below.

| Binary Numbers |   | Addition    |

|----------------|---|-------------|

| 0              | 0 | 0           |

| 0              | 1 | 1           |

| 1              | 0 | 1           |

| 1              | 1 | 0; Carry →1 |

Let us take an example of two binary numbers and add them.

For example: Add 1101<sub>2</sub> and 1001<sub>2</sub>.

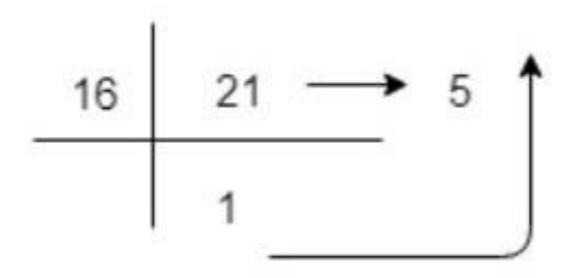

#### Solution:

# **Binary Subtraction**

Subtracting two binary numbers will give us a binary number itself. It is also a straightforward method. Subtraction of two single-digit binary number is given in the table below.

| Binary Number | s | Subtraction |

|---------------|---|-------------|

| 0             | 0 | 0           |

| 0             | 1 | 1; Borrow 1 |

| 1             | 0 | 1           |

| 1             | 1 | 0           |

Let us take an example of two binary numbers and subtract them.

Example: Subtract 1101<sub>2</sub>, and 1010<sub>2</sub>.

# Solution:

## **Binary Multiplication**

The multiplication process is the same for the binary numbers as it is for numerals. Let us understand it with example.

Example: Multiply 1101<sub>2</sub> and 1010<sub>2</sub>.

Solution:

**Binary Division**

The binary division is similar to the decimal number division method. We will learn with an example here.

**Example:** Divide 1010<sub>2</sub> by 10<sub>2</sub>

Solution:

Uses of Binary Number System

Binary numbers are commonly used in computer applications. All the coding and languages in computers such as C, C++, Java, etc. use binary digits 0 and 1 to write a program or encode any digital data. The computer understands only the coded language. Therefore these 2-digit number system is used to represent a set of data or information in discrete bits of information.

**Problems and Solutions**

Let us practice some of the problems for better understanding:

Question 1: What is binary number 1.1 in decimal?

Solution:

Step 1: 1 on the left-hand side is on the one's position, so it's 1.

Step 2: The one on the right-hand side is in halves, so it's

$1 \times \frac{1}{2}$

**Step 3:** so, 1.1 = 1.5 in decimal.

Question 2: Write 10.11<sub>2</sub> in Decimal?

Solution:

$$10.11 = 1 \times (2)^{1} + 0 (2)^{0} + 1 (\frac{1}{2})^{1} + 1(\frac{1}{2})^{2}$$

$$= 2 + 0 + \frac{1}{2} + \frac{1}{2}$$

$$= 2.75$$

So, 10.11 is 2.75 in Decimal.

Keep visiting BYJU'S to explore and learn more such Math-related topics in a fun and engaging way.

Frequently Asked Questions – FAQs

# What is a binary number system?

A number system where a number is represented by using only two digits (0 and 1) with a base 2 is called a binary number system. For example, 10012 is a binary number.

#### What is a bit?

A bit is a single digit in the binary number. For example, 101 is three-bit binary numbers, where 1, 0 and 1 are the bits.

How to convert a decimal number into a binary number? Give an example.

To convert a decimal number into its equivalent binary number, we divide the decimal number by 2 each time, till we get 0 as a dividend. Let us take an example to convert 1310 into a binary number.

13 ÷ 2: 6 and remainder 1

6 ÷ 2: 3 and remainder 0

3 ÷ 2: 1 and remainder 1

1 ÷ 2: 0 and remainder 1

Now we take the bits from the last remainder to first remainder, i.e.(MSB to LSB). Hence.

$13_{10} = 1101^2$

# What is the use of binary numbers?

Binary numbers are commonly used in computer architecture. Since the computer understands only the language of two digits 0's and 1's, therefore the programming is done using a binary number system.

What is the value of 163 in binary?

The value of 163 in binary is 10100011.

How is 200 represented in binary?

200 is the decimal number. The binary form of 200 is 110010002.

#### Octal

**Octal Number System** has a base of eight and uses the number from 0 to 7. The octal numbers, in the number system, are usually represented by binary numbers when they are grouped in pair of three. For example, 12<sub>8</sub> is expressed as 001010<sub>2</sub>, where 1 is equivalent to 001 and 2 is equivalent to 010.

# **Octal Number System**

#### Base - 8

# Octal Symbol - 0, 1, 2, 3, 4, 5, 6 and 7

#### **Table of Contents:**

- Definition

- Chart

- Decimal to Octal

- Octal to Decimal

- Binary to Octal

- Octal to Hexadecimal

- Octal Multiplication Table

- Applications

- FAQs

Apart from octal number system, there are other number systems in Maths, such as:

- Binary Number System

- Hexadecimal Number System

- Decimal Number System

# **Definition**

A number system which has its base as 'eight' is called an Octal number system. It uses numbers from 0 to 7. Let us take an example, to understand the concept. As we said, any number with base 8 is an octal number like  $24_8$ ,  $109_8$ ,  $55_8$ , etc.

Like Octal number is represented with base 8, in the same way, a binary number is represented with base 2, decimal number with base 10 and the hexadecimal number is represented with base 16. Examples for these number systems are:

- 22<sub>2</sub> is a binary number

- 100<sub>10</sub> is a decimal number

- 40<sub>16</sub> is a hexadecimal number

If we solve an octal number, each place is a power of eight.

•

$$124_8 = 1 \times 8^2 + 2 \times 8^1 + 4 \times 8^0$$

#### **Octal Numbers Chart**

We use only 3 bits to represent Octal Numbers. Each group will have a distinct value between 000 and 111.

| Octal Digital Value | Binary Equivalent |

|---------------------|-------------------|

| 0                   | 000               |

| 1                   | 001               |

| 2                   | 010               |

| 3                   | 011               |

| 4                   | 100               |

| 5                   | 101               |

| 6                   | 110               |

| 7                   | 111               |

#### **Decimal to Octal Number**

To convert decimal to octal number, octal dabble method is used. In this method, the decimal number is divided by 8 each time, it yields or gives a remainder. The first remainder we get is the least significant digit(LSD) and the last remainder is the most significant digit(MSD). Let us understand the conversion with the help example.

# **Solved Example**

**Problem**: Suppose 560 is a decimal number. Convert it into an octal number.

**Solution**: If 560 is a decimal number, then,

560/8=70 and remainder is 0

70/8=8 and remainder is 6

8/8=1 and remainder is 0

And 1/8=0 and remainder is 1

So the octal number starts from MSD to LSD, i.e. 1060

Therefore,  $560_{10} = 1060_8$

**Problem:** Convert 0.52 into an octal number.

**Solution:** The fraction part of the decimal number has to be multiplied by 8.

$0.52 \times 8 = 0.16$  with carry 4

$0.16 \times 8 = 0.28$  with carry 1

$0.28 \times 8=0.24$  with carry 2

$0.24 \times 8 = 0.92$  with carry 1

So, for the fractional octal number, we read the generated carry from up to down.

Therefore, 4121 is the octal number.

#### **Octal to Decimal Number**

Let us learn here, conversion of Octal number to Decimal Number or base 8 to base 10.

# Solved Example

**Example:** Suppose 215<sub>8</sub> is an octal number, then it's decimal form will be,

$$215_8 = 2 \times 8^2 + 1 \times 8^1 + 5 \times 8^0$$

$$= 2 \times 64 + 1 \times 8 + 5 \times 1 = 128 + 8 + 5$$

$$= 141_{10}$$

**Example:** Let 125 is an octal number denoted by 125<sub>8</sub>. Find the decimal number.

$$125_8 = 1 \times 8^2 + 2 \times 8^1 + 5 \times 8^0$$

$$= 1 \times 64 + 2 \times 8 + 5 \times 1 = 64 + 16 + 5$$

$$= 85_{10}$$

# **Binary To Octal Number**

A binary number can be converted into an octal number, with the help of the belowgiven table.

| Octal Number | Equivalent Binary Number |

|--------------|--------------------------|

| 0            | 0                        |

| 1            | 1                        |

| 2            | 10                       |

| 3            | 11                       |

| 4 | 100 |

|---|-----|

| 5 | 101 |

| 6 | 110 |

| 7 | 111 |

Solved Example

**Example:** Convert (100010)<sub>2</sub> to octal number.

**Solution:** With the help of the table we can write,

100→4

and 010→2

Therefore, $(100010)_2 = 42$

Similarly, we can convert an octal number to binary number with the help of the table.

#### **Octal to Hexadecimal Number**

Hexadecimal number consist of numbers and alphabets. It is represented with base 16. The numbers from 0-9 are represented in the usual form, but from 10 to 15, it is denoted as A, B, C, D, E, F. Conversion of the octal number to hexadecimal requires two steps.

- First, convert octal number to decimal number.

- Then, convert decimal number to hexadecimal number.

Let us understood with the help of an example. We will take the same example, where we have converted octal number to decimal, such as;

$$(215)_8 = (45)_{10}$$

Now, convert (45)<sub>10</sub> into a hexadecimal number by dividing 45 by 16 until you get remainder less than 16.

Therefore, we can write,  $(45)_{10} = (2D)_{16}$

Or

$$(215)_8 = (2D)_{16}$$

# Octal Multiplication Table

| * |   | ^  | 4 | • | _   | 4 | _ | ^ | <b>-</b> |

|---|---|----|---|---|-----|---|---|---|----------|

|   | ( | () | 1 |   | - 3 | 4 | 5 | h | /        |

|   |   | •  | • | _ | •   | • | • | J | •        |

|   |   |    |   |   |     |   |   |   |          |

| 0 | 0 | 0 | 0  | 0  | 0  | 0  | 0  | 0  |

|---|---|---|----|----|----|----|----|----|

| 1 | 0 | 1 | 2  | 3  | 4  | 5  | 6  | 7  |

| 2 | 0 | 2 | 4  | 6  | 10 | 12 | 14 | 16 |

| 3 | 0 | 3 | 6  | 11 | 14 | 17 | 22 | 25 |

| 4 | 0 | 4 | 10 | 14 | 20 | 24 | 30 | 34 |

| 5 | 0 | 5 | 12 | 17 | 24 | 31 | 36 | 43 |

| 6 | 0 | 6 | 14 | 22 | 30 | 36 | 44 | 52 |

| 7 | 0 | 7 | 16 | 25 | 34 | 43 | 52 | 61 |

# **Applications**

The octal Number system is widely used in computer application sectors and also in the aviation sector to use the number in the form of code.

Based on octal number system applications, several computing systems are developed. All the modern generation computing system uses 16-bit, 32-bit or 64-bit word which is further divided into 8-bit words. Similarly, for various programming languages, octal numbers are used to do coding or to write the encrypted language, which is only understood by the computing machine.

Also in the aviation sector or field or say aviation industry, Transponders used in the aircraft transmits a code which is expressed as four octal digit number. These codes are interrogated by ground radar.

Also, study-related topics on number systems by downloading BYJU'S -The Learning App.

Frequently Asked Questions – FAQs

# What is an octal number system?

A number system expressed with base-8 and whose range is from 0 to 8 only, it is called octal number system. It is represented as N8.

#### What is the use of octal numbers?

The octal Number system is widely used in computer application sectors. All the modern generation computing system uses 16-bit, 32-bit or 64-bit word which is further divided

into 8-bit words. Also in the aviation sector the octal numbers are used in the form of code.

# What is the importance of octal number system?

Since, the octal numbers uses less number of digits as compared to decimal numbers and hexadecimal numbers, therefore it is easy to do computations in fewer steps and also less chances of occurrence of error.

#### What is the octal form of decimal number 19?

To convert a decimal number into octal number, we need to divide the given decimal number by 8 and until output is 0. At last we need to write the remainder from LSD to MSD in reverse order.

```

19/8 = 2, Remainder = 3 2/8 = 0, Remainder = 2 Therefore, 19_{10} = 23_8

```

# What are 4 types of number system?

Binary number system

Octal Number system

Decimal number system

Hexadecimal number system

```

What is 13_8 in binary?

```

```

For octal number 13, 1 \rightarrow 001 3 \rightarrow 011 Therefore, clubbing both the numbers we get: 13_8 = 001011_2 Or 13_8 = 1011_2

```

What is the binary number 1111 equivalent to in octal number system?

```

1111 can be written in group of three digits by adding 0's, such as; 001111 \to 001 111 \to 17 (1111)<sub>2</sub> \to (17)<sub>2</sub>

```

#### Hexadecimal

Hexadecimal Number System is one the type of Number Representation techniques, in which there value of base is 16. That means there are only 16 symbols or possible digit values, there are 0, 1, 2, 3, 4, 5, 6, 7, 8, 9, A, B, C, D, E, F. Where A, B, C, D, E and F are single bit representations of decimal value 10, 11, 12, 13, 14 and 15 respectively. It

requires only 4 bits to represent value of any digit. Hexadecimal numbers are indicated by the addition of either an 0x prefix or an h suffix.

Position of every digit has a weight which is a power of 16. Each position in the Hexadecimal system is 16 times more significant than the previous position, that means numeric value of an hexadecimal number is determined by multiplying each digit of the number by the value of the position in which the digit appears and then adding the products. So, it is also a positional (or weighted) number system.

# **Representation of Hexadecimal Number**

Each Hexadecimal number can be represented using only 4 bits, with each group of bits having a distich values between 0000 (for 0) and 1111 (for F = 15 = 8+4+2+1). The equivalent binary number of Hexadecimal number are as given below.

| Hex digit | 1    | 0    | 2    | 3    | 4    | 5    | 6    | 7    |

|-----------|------|------|------|------|------|------|------|------|

| Binary    | 0000 | 0001 | 0010 | 0011 | 0100 | 0101 | 0110 | 0111 |

| Hex digit | 8    | 9    | A = 10 | B = 11 | C = 12 | D = 13 | E = 14 | F = 15 |

|-----------|------|------|--------|--------|--------|--------|--------|--------|

| Binary    | 1000 | 1001 | 1010   | 1011   | 1100   | 1101   | 1110   | 1111   |

Hexadecimal number system is similar to Octal number system. Hexadecimal number system provides convenient way of converting large binary numbers into more compact and smaller groups.

| Most Significant Bit (MSB) | Hex             | Point           | Leas             | t Significant    | Bit (LSB)        |

|----------------------------|-----------------|-----------------|------------------|------------------|------------------|

| 16 <sup>2</sup>            | 16 <sup>1</sup> | 16 <sup>0</sup> | 16 <sup>-1</sup> | 16 <sup>-2</sup> | 16 <sup>-3</sup> |

| 256                        | 16              | 1               | 1/16             | 1/256            | 1/4096           |

Since base value of Hexadecimal number system is 16, so there maximum value of digit is 15 and it can not be more than 15. In this number system, the successive positions to the left of the hexadecimal point having weights of 16<sup>1</sup>, 16<sup>1</sup>, 16<sup>2</sup>, 16<sup>3</sup> and so on. Similarly, the successive positions to the right of the hexadecimal point having weights of 16<sup>-1</sup>, 16<sup>-2</sup>, 16<sup>-3</sup> and so on. This is called base power of 16. The decimal value of any

hexadecimal number can be determined using sum of product of each digit with its positional value.

**Example-1** – The number 512 is interpreted as

$$512=2x16^2+0x16^1+0x16^0=200$$

Here, right most bit 0 is the least significant bit (LSB) and left most bit 2 is the most significant bit (MSB).

**Example-2** – The number 2015.0625 is interpreted as

$$2015.0625 = 7x16^{2} + 13x16^{1} + 15x16^{0} + 1x16^{-1} = 7DF.10$$

Here, right most bit 0 is the least significant bit (LSB) and left most bit 7 is the most significant bit (MSB).

**Example-3** A a decimal number 21 to represent in Hexadecimal representation

$(21)_{10}=1x16^{1}+5x16^{0}=(15)_{16}$ So, decimal value 21 is equivalent to 15 in Hexadecimal Number System.

# **Applications of Hexadecimal Number System**

Hexadecimal Number System is commonly used in Computer programming and Microprocessors. It is also helpful to describe colors on web pages. Each of the three primary colors (i.e., red, green and blue) is represented by two hexadecimal digits to create 255 possible values, thus resulting in more than 16 million possible colors. Hexadecimal number system is used to describe locations in memory for every byte. These hexadecimal numbers are also easier to read and write than binary or decimal numbers for Computer Professionals.

# **Advantages and Disadvantages**

The main advantage of using Hexadecimal numbers is that it uses less memory to store more numbers, for example it store 256 numbers in two digits whereas decimal number stores 100 numbers in two digits. This number system is also used to represent Computer memory addresses. It uses only 4 bits to represent any digit in binary and easy to convert from hexadecimal to binary and vice-versa. It is easier to handle input and output in the hexadecimal form. There is wide number of advantages in data science field, artificial intelligence and machine learning.

The major disadvantage of Hexadecimal number system is that it may not an easy to read and write for people, and also difficult to perform operations like multiplications, divisions using hexadecimal number system. Hexadecimal numbers is most difficult number system for dealing with Computer's data.

# 15's and 16's Complement of Hexadecimal (Base-16) Number

Simply, 15's complement of a hexadecimal number is the subtraction of it's each digits from F(=15). For example, 15's complement of hexadecimal number 2030 is FFFF - 2030 = DFCF.

16's complement of hexadecimal number is 15's complement of given number plus 1 to the least significant bit (LSB). For example 8's complement of hexadecimal number 2020 is (FFFF - 2030) + 1 = DFDF + 1 = DFE0. Please note that maximum digit of hexadecimal number system is F(=15), so addition of F+1 will be 0 with carry 1.

## Character Codes (BCD, ASCII, EBCDIC)

Computers and digital circuits processes information in the binary format. Each character is assigned 7 or 8 bit binary code to indicate its character which may be numeric, alphabet or special symbol. Example - Binary number 1000001 represents 65(decimal) in straight binary code, alphabet A in ASCII code and 41(decimal) in BCD code.

## Types of codes

## **BCD** (Binary-Coded Decimal) code:

Four-bit code that represents one of the ten decimal digits from 0 to 9.

Example - (37)10 is represented as 0011 0111 using BCD code, rather than (100101)2 in straight binary code.

Thus BCD code requires more bits than straight binary code.

Still it is suitable for input and output operations in digital systems.

Note: 1010, 1011, 1100, 1101, 1110, and 1111 are INVALID CODE in BCD code.

ASCII (American Standard Code Information Interchange) code:

It is 7-bit or 8-bit alphanumeric code.

7-bit code is standard ASCII supports 127 characters.

Standard ASCII series starts from 00h to 7Fh, where 00h-1Fh are used as control characters and 20h-7Fh as graphics symbols.

8-bit code is extended ASCII supports 256 symbols where special graphics and math's symbols are added.

Extended ASCII series starts from 80h to FFh.

EBCDIC (Extended Binary Coded Decimal Interchange Code) code

8-bit alphanumeric code developed by IBM, supports 256 symbols.

It was mainly used in IBM mainframe computers.

Gray code

Differs from leading and following number by a single bit.

Gray code for 2 is 0011 and for 3 is 0010.

No weights are assigned to the bit positions.

Extensively used in shaft encoders.

Excess-3 code

4-bit code is obtained by adding binary 0011 to the natural BCD code of the digit.

Example - decimal 2 is coded as 0010 + 0011 = 0101 as Excess-3 code.

It not weighted code.

Its self-complimenting code, means 1's complement of the coded number yields 9's complement of the number itself.

Used in digital system for performing substraction operations.

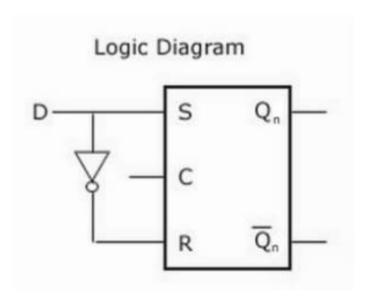

# Logic gates

Logic gates are the basic building blocks of any digital system. It is an electronic circuit having one or more than one input and only one output. The relationship between the input and the output is based on a **certain logic**. Based on this, logic gates are named as AND gate, OR gate, NOT gate etc.

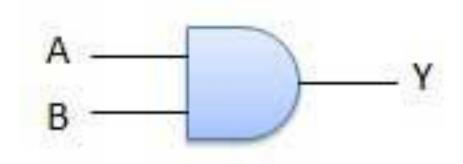

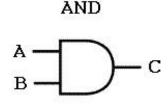

## **AND Gate**

A circuit which performs an AND operation is shown in figure. It has n input ( $n \ge 2$ ) and one output.

# Logic diagram

| Inpu | its | Output |

|------|-----|--------|

| А    | В   | AB     |

| 0    | 0   | 0      |

| 0    | 1   | 0      |

| 1    | 0   | 0      |

| 1    | 1   | 1      |

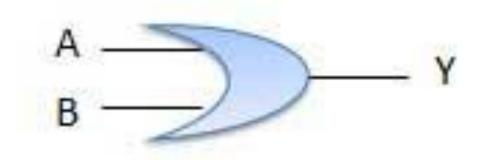

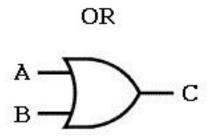

# **OR Gate**

A circuit which performs an OR operation is shown in figure. It has n input ( $n \ge 2$ ) and one output.

# Logic diagram

| Inpu | ıts | Output |

|------|-----|--------|

| Α    | В   | A+B    |

| 0    | 0   | 0      |

| 0    | 1   | 1      |

| 1    | 0   | 1      |

| 1    | 1   | 1      |

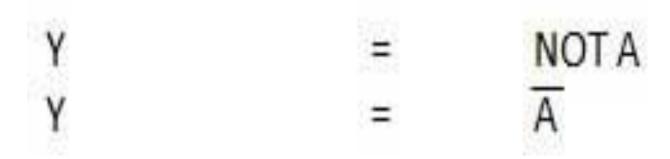

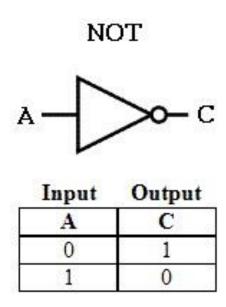

# **NOT Gate**

NOT gate is also known as **Inverter**. It has one input A and one output Y.

# Logic diagram

| Inputs | Output |

|--------|--------|

| Α      | В      |

| 0      | 1      |

| 1      | 0      |

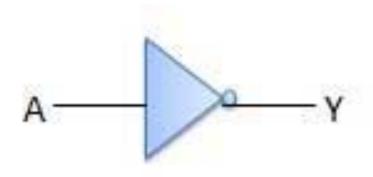

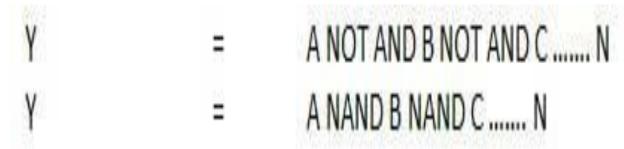

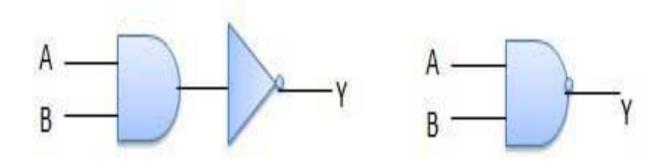

# **NAND Gate**

A NOT-AND operation is known as NAND operation. It has n input (n  $\geq$  2) and one output.

# Logic diagram

| Inpu | its | Output |

|------|-----|--------|

| Α    | В   | AB     |

| 0    | 0   | 1      |

| 0    | 1   | 1      |

| 1    | 0   | 1      |

| 1    | 1   | 0      |

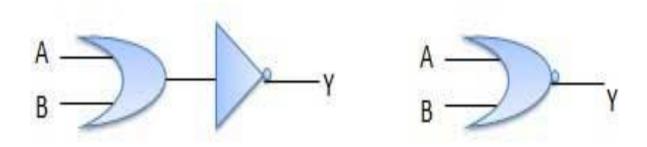

# **NOR Gate**

A NOT-OR operation is known as NOR operation. It has n input (n  $\geq$  2) and one output.

# Logic diagram

# **Truth Table**

| Inpu | its | Output |

|------|-----|--------|

| Α    | В   | A+B    |

| 0    | 0   | 1      |

| 0    | 1   | 0      |

| 1    | 0   | 0      |

| 1    | 1   | 0      |

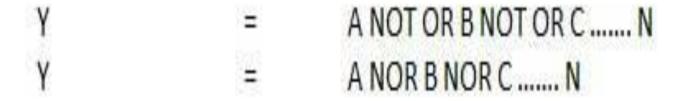

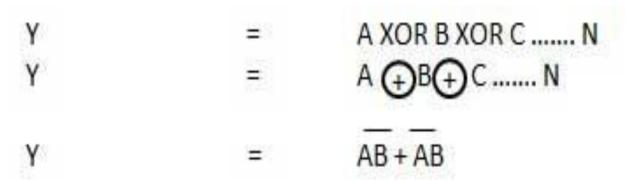

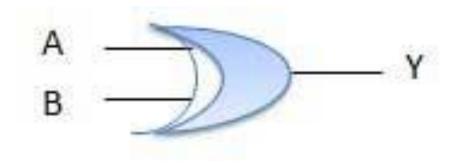

# **XOR Gate**

XOR or Ex-OR gate is a special type of gate. It can be used in the half adder, full adder and subtractor. The exclusive-OR gate is abbreviated as EX-OR gate or sometime as X-OR gate. It has n input ( $n \ge 2$ ) and one output.

# Logic diagram

# **Truth Table**

| 100 | Inpu | ts | Output  |

|-----|------|----|---------|

|     | Α    | В  | A (+) B |

|     | 0    | 0  | 0       |

|     | 0    | 1  | 1       |

|     | 1    | 0  | 1       |

|     | 1    | 1  | 0       |

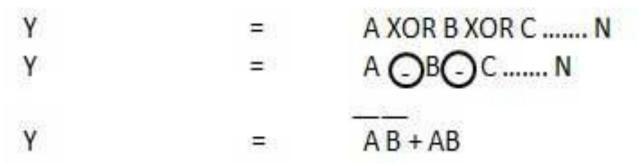

# **XNOR Gate**

XNOR gate is a special type of gate. It can be used in the half adder, full adder and subtractor. The exclusive-NOR gate is abbreviated as EX-NOR gate or sometime as X-NOR gate. It has n input ( $n \ge 2$ ) and one output.

# Logic diagram

# **Truth Table**

| Inpu | ıts | Output |

|------|-----|--------|

| Α    | В   | A - B  |

| 0    | 0   | 1      |

| 0    | 1   | 0      |

| 1    | 0   | 0      |

| 1    | 1   | 1      |

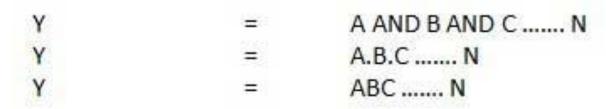

# **Boolean Algebra**

Boolean Algebra is used to analyze and simplify the digital (logic) circuits. It uses only the binary numbers i.e. 0 and 1. It is also called as Binary Algebra or logical Algebra. Boolean algebra was invented by George Boole in 1854.

# Rule in Boolean Algebra

Following are the important rules used in Boolean algebra.

- Variable used can have only two values. Binary 1 for HIGH and Binary 0 for LOW.

- Complement of a variable is represented by an overbar (-). Thus, complement of variable B is represented as  $\overline{B}$ . Thus if B = 0 then  $\overline{B}$  = 1 and B = 1 then  $\overline{B}$  = 0.

- ORing of the variables is represented by a plus (+) sign between them. For example ORing of A, B, C is represented as A + B + C.

- Logical ANDing of the two or more variable is represented by writing a dot between them such as A.B.C. Sometime the dot may be omitted like ABC.

# **Boolean Laws**

There are six types of Boolean Laws.

# Commutative law

Any binary operation which satisfies the following expression is referred to as commutative operation.

(i)

$$A.B = B.A$$

(ii)  $A + B = B + A$

Commutative law states that changing the sequence of the variables does not have any effect on the output of a logic circuit.

## Associative law

This law states that the order in which the logic operations are performed is irrelevant as their effect is the same.

(i)

$$(A.B).C = A.(B.C)$$

(ii)  $(A+B)+C=A+(B+C)$

#### Distributive law

Distributive law states the following condition.

$$A.(B + C) = A.B + A.C$$

## AND law

These laws use the AND operation. Therefore they are called as AND laws.

(i)

$$A.0 = 0$$

(ii)

$$A.1 = A$$

(iv)

$$A.\overline{A} = 0$$

## **OR** law

These laws use the OR operation. Therefore they are called as **OR** laws.

(i)

$$A + 0 = A$$

(ii)

$$A + 1 = 1$$

$$(iii) A + A = A$$

(iv)

$$A + \overline{A} = 1$$

## **INVERSION** law

This law uses the NOT operation. The inversion law states that double inversion of a variable results in the original variable itself.

## Important Boolean Theorems

Following are few important boolean Theorems.

| Boolean function/theorems | Description                                                         |

|---------------------------|---------------------------------------------------------------------|

| Boolean Functions         | Boolean Functions and Expressions, K-Map and NAND Gates realization |

| De Morgan's Theorems      | De Morgan's Theorem 1 and Theorem 2                                 |

## K-map simplification

In previous chapters, we have simplified the Boolean functions using Boolean postulates and theorems. It is a time consuming process and we have to re-write the simplified expressions after each step.

To overcome this difficulty, Karnaugh introduced a method for simplification of Boolean functions in an easy way. This method is known as Karnaugh map method or K-map method. It is a graphical method, which consists of 2<sup>n</sup> cells for 'n' variables. The adjacent cells are differed only in single bit position.

## K-Maps for 2 to 5 Variables

K-Map method is most suitable for minimizing Boolean functions of 2 variables to 5 variables. Now, let us discuss about the K-Maps for 2 to 5 variables one by one.

## 2 Variable K-Map

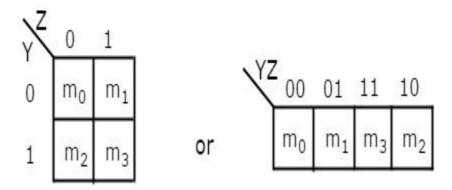

The number of cells in 2 variable K-map is four, since the number of variables is two. The following figure shows **2 variable K-Map**.

There is only one possibility of grouping 4 adjacent min terms.

• The possible combinations of grouping 2 adjacent min terms are {(m<sub>0</sub>, m<sub>1</sub>), (m<sub>2</sub>, m<sub>3</sub>), (m<sub>0</sub>, m<sub>2</sub>) and (m<sub>1</sub>, m<sub>3</sub>)}.

## 3 Variable K-Map

The number of cells in 3 variable K-map is eight, since the number of variables is three. The following figure shows **3 variable K-Map**.

- There is only one possibility of grouping 8 adjacent min terms.

- The possible combinations of grouping 4 adjacent min terms are {(m<sub>0</sub>, m<sub>1</sub>, m<sub>3</sub>, m<sub>2</sub>), (m<sub>4</sub>, m<sub>5</sub>, m<sub>7</sub>, m<sub>6</sub>), (m<sub>0</sub>, m<sub>1</sub>, m<sub>4</sub>, m<sub>5</sub>), (m<sub>1</sub>, m<sub>3</sub>, m<sub>5</sub>, m<sub>7</sub>), (m<sub>3</sub>, m<sub>2</sub>, m<sub>7</sub>, m<sub>6</sub>) and (m<sub>2</sub>, m<sub>0</sub>, m<sub>6</sub>, m<sub>4</sub>)}.

- The possible combinations of grouping 2 adjacent min terms are  $\{(m_0, m_1), (m_1, m_3), (m_3, m_2), (m_2, m_0), (m_4, m_5), (m_5, m_7), (m_7, m_6), (m_6, m_4), (m_0, m_4), (m_1, m_5), (m_3, m_7)$  and  $\{(m_1, m_2, m_6)\}$ .

- If x=0, then 3 variable K-map becomes 2 variable K-map.

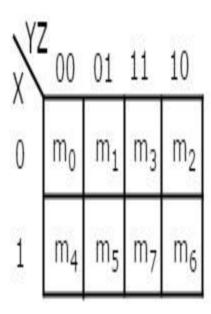

## 4 Variable K-Map

The number of cells in 4 variable K-map is sixteen, since the number of variables is four. The following figure shows **4 variable K-Map**.

- There is only one possibility of grouping 16 adjacent min terms.

- Let R<sub>1</sub>, R<sub>2</sub>, R<sub>3</sub> and R<sub>4</sub> represents the min terms of first row, second row, third row and fourth row respectively. Similarly, C<sub>1</sub>, C<sub>2</sub>, C<sub>3</sub> and C<sub>4</sub> represents the min terms of first column, second column, third column and fourth column respectively. The possible combinations of grouping 8 adjacent min terms are {(R<sub>1</sub>, R<sub>2</sub>), (R<sub>2</sub>, R<sub>3</sub>), (R<sub>3</sub>, R<sub>4</sub>), (R<sub>4</sub>, R<sub>1</sub>), (C<sub>1</sub>, C<sub>2</sub>), (C<sub>2</sub>, C<sub>3</sub>), (C<sub>3</sub>, C<sub>4</sub>), (C<sub>4</sub>, C<sub>1</sub>)}.

- If w=0, then 4 variable K-map becomes 3 variable K-map.

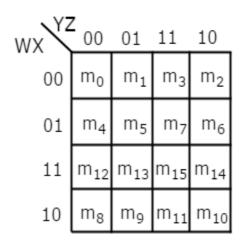

## 5 Variable K-Map

The number of cells in 5 variable K-map is thirty-two, since the number of variables is 5. The following figure shows 5 variable K-Map.

| V=0   |                 |                 |                 |                 |    |                 | V=              | =1              |                 |

|-------|-----------------|-----------------|-----------------|-----------------|----|-----------------|-----------------|-----------------|-----------------|

| WX YZ | 00              | 01              | 11              | 10              | WX | 00              | 01              | 11              | 10              |

| 00    | m <sub>0</sub>  | m <sub>1</sub>  | m <sub>3</sub>  | m <sub>2</sub>  | 00 | m <sub>16</sub> | m <sub>17</sub> | m <sub>19</sub> | m <sub>18</sub> |

| 01    | m <sub>4</sub>  | m <sub>5</sub>  | m <sub>7</sub>  | m <sub>6</sub>  | 01 | m <sub>20</sub> | m <sub>21</sub> | m <sub>23</sub> | m <sub>22</sub> |

| 11    | m <sub>12</sub> | m <sub>13</sub> | m <sub>15</sub> | m <sub>14</sub> | 11 | m <sub>28</sub> | m <sub>29</sub> | m <sub>31</sub> | m <sub>30</sub> |

| 10    | m <sub>8</sub>  | m <sub>9</sub>  | m <sub>11</sub> | m <sub>10</sub> | 10 | m <sub>24</sub> | m <sub>25</sub> | m <sub>27</sub> | m <sub>26</sub> |

- There is only one possibility of grouping 32 adjacent min terms.

- There are two possibilities of grouping 16 adjacent min terms. i.e., grouping of min terms from m<sub>0</sub> to m<sub>15</sub> and m<sub>16</sub> to m<sub>31</sub>.

- If v=0, then 5 variable K-map becomes 4 variable K-map.

In the above all K-maps, we used exclusively the min terms notation. Similarly, you can use exclusively the Max terms notation.

## Minimization of Boolean Functions using K-Maps

If we consider the combination of inputs for which the Boolean function is '1', then we will get the Boolean function, which is in standard sum of products form after simplifying the K-map.

Similarly, if we consider the combination of inputs for which the Boolean function is '0', then we will get the Boolean function, which is in **standard product of sums** form after simplifying the K-map.

Follow these rules for simplifying K-maps in order to get standard sum of products form.

- Select the respective K-map based on the number of variables present in the Boolean function.

- If the Boolean function is given as sum of min terms form, then place the ones at respective min term cells in the K-map. If the Boolean function is given as sum of products form, then place the ones in all possible cells of K-map for which the given product terms are valid.

- Check for the possibilities of grouping maximum number of adjacent ones. It should be powers of two. Start from highest power of two and upto least power of two. Highest power is equal to the number of variables considered in K-map and least power is zero.

- Each grouping will give either a literal or one product term. It is known as prime implicant. The prime implicant is said to be essential prime implicant, if atleast single '1' is not covered with any other groupings but only that grouping covers.

- Note down all the prime implicants and essential prime implicants. The simplified Boolean function contains all essential prime implicants and only the required prime implicants.

**Note 1** – If outputs are not defined for some combination of inputs, then those output values will be represented with don't care symbol 'x'. That means, we can consider them as either '0' or '1'.

**Note 2** – If don't care terms also present, then place don't cares 'x' in the respective cells of K-map. Consider only the don't cares 'x' that are helpful for grouping maximum number of adjacent ones. In those cases, treat the don't care value as '1'.

## Example

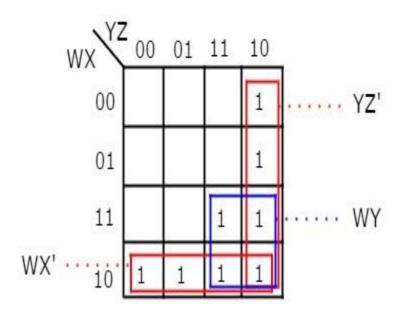

Let us **simplify** the following Boolean function, **f**W,X,Y,ZW,X,Y,Z= **WX'Y'** + **WY + W'YZ'** using K-map.

The given Boolean function is in sum of products form. It is having 4 variables W, X, Y & Z. So, we require **4 variable K-map**. The **4 variable K-map** with ones corresponding to the given product terms is shown in the following figure.

| WX YZ | 00 | 01 | 11 | 10 |

|-------|----|----|----|----|

| 00    |    |    |    | 1  |

| 01    |    |    |    | 1  |

| 11    |    |    | 1  | 1  |

| 10    | 1  | 1  | 1  | 1  |

Here, 1s are placed in the following cells of K-map.

- The cells, which are common to the intersection of Row 4 and columns 1 & 2 are corresponding to the product term, **WX'Y'**.

- The cells, which are common to the intersection of Rows 3 & 4 and columns 3 & 4 are corresponding to the product term, WY.

- The cells, which are common to the intersection of Rows 1 & 2 and column 4 are corresponding to the product term, **W'YZ'**.

There are no possibilities of grouping either 16 adjacent ones or 8 adjacent ones. There are three possibilities of grouping 4 adjacent ones. After these three groupings, there is no single one left as ungrouped. So, we no need to check for grouping of 2 adjacent ones. The **4 variable K-map** with these three **groupings** is shown in the following figure.

Here, we got three prime implicants WX', WY & YZ'. All these prime implicants are **essential** because of following reasons.

- Two ones (m<sub>8</sub> & m<sub>9</sub>) of fourth row grouping are not covered by any other groupings. Only fourth row grouping covers those two ones.

- Single one  $(m_{15})$  of square shape grouping is not covered by any other groupings. Only the square shape grouping covers that one.

- Two ones (m<sub>2</sub> & m<sub>6</sub>) of fourth column grouping are not covered by any other groupings. Only fourth column grouping covers those two ones.

Therefore, the simplified Boolean function is

$$f = WX' + WY + YZ'$$

Follow these **rules for simplifying K-maps** in order to get standard product of sums form.

- Select the respective K-map based on the number of variables present in the Boolean function.

- If the Boolean function is given as product of Max terms form, then place the zeroes at respective Max term cells in the K-map. If the Boolean function is given as product of sums form, then place the zeroes in all possible cells of K-map for which the given sum terms are valid.

- Check for the possibilities of grouping maximum number of adjacent zeroes. It should be powers of two. Start from highest power of two and upto least power of two. Highest power is equal to the number of variables considered in K-map and least power is zero.

- Each grouping will give either a literal or one sum term. It is known as prime implicant. The prime implicant is said to be essential prime implicant, if

atleast single '0' is not covered with any other groupings but only that grouping covers.

Note down all the prime implicants and essential prime implicants. The simplified Boolean function contains all essential prime implicants and only the required prime implicants.

**Note** – If don't care terms also present, then place don't cares 'x' in the respective cells of K-map. Consider only the don't cares 'x' that are helpful for grouping maximum number of adjacent zeroes. In those cases, treat the don't care value as '0'.

## Example

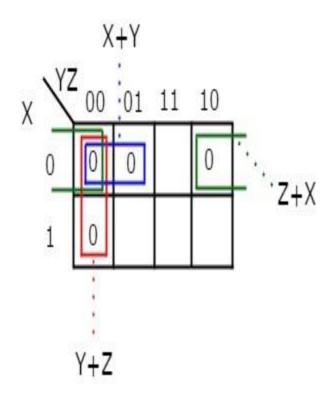

Let us **simplify** the following Boolean function,  $f(X,Y,Z) = \prod M(0,1,2,4) f(X,Y,Z) = \prod M(0,1,2,4)$  using K-map.

The given Boolean function is in product of Max terms form. It is having 3 variables X, Y & Z. So, we require 3 variable K-map. The given Max terms are  $M_0$ ,  $M_1$ ,  $M_2$  &  $M_4$ . The 3 **variable K-map** with zeroes corresponding to the given Max terms is shown in the following figure.

There are no possibilities of grouping either 8 adjacent zeroes or 4 adjacent zeroes. There are three possibilities of grouping 2 adjacent zeroes. After these three groupings, there is no single zero left as ungrouped. The **3 variable K-map** with these three **groupings** is shown in the following figure.

Here, we got three prime implicants X + Y, Y + Z & Z + X. All these prime implicants are **essential** because one zero in each grouping is not covered by any other groupings except with their individual groupings.

Therefore, the **simplified Boolean function** is

$$f = X+YX+Y.Y+ZY+Z.Z+XZ+X$$

In this way, we can easily simplify the Boolean functions up to 5 variables using K-map method. For more than 5 variables, it is difficult to simplify the functions using K-Maps. Because, the number of **cells** in K-map gets **doubled** by including a new variable.

Due to this checking and grouping of adjacent ones mintermsminterms or adjacent zeros MaxtermsMaxterms will be complicated. We will discuss **Tabular method** in next chapter to overcome the difficulties of K-map method.

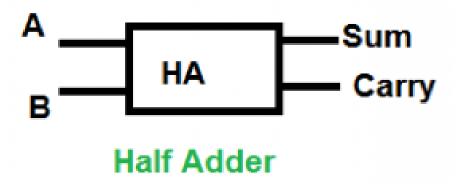

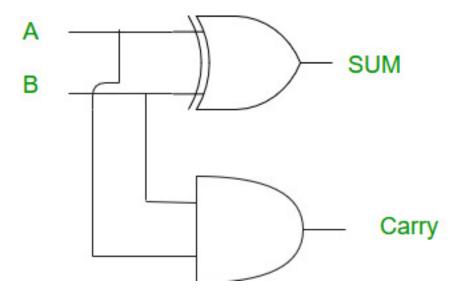

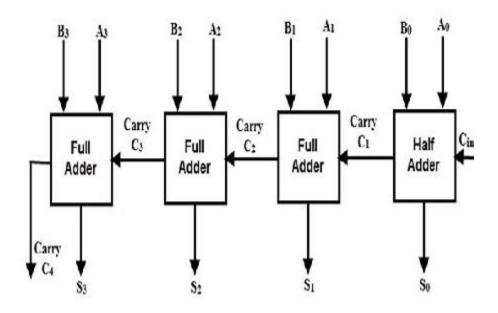

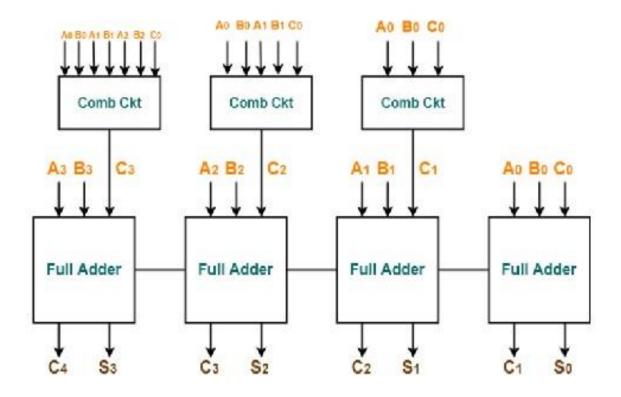

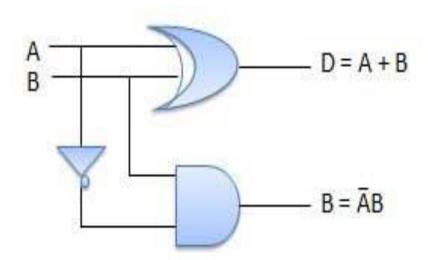

## Half Adder

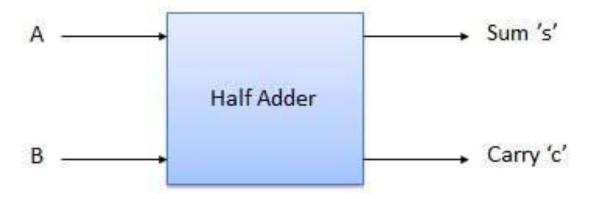

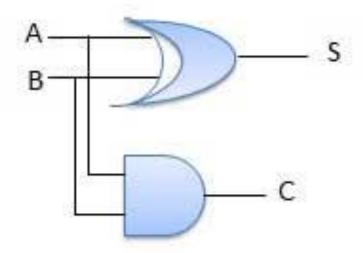

The addition of 2 bits is done using a combination circuit called Half adder. The input variables are augend and addend bits and output variables are sum & carry bits. A and B are the two input bits.

## **Truth Table:**

| A | В | Sum | Carry |

|---|---|-----|-------|

| 0 | 0 | 0   | 0     |

| 0 | 1 | 1   | 0     |

| 1 | 0 | 1   | 0     |

| 1 | 1 | 0   | 1     |

Logical Expression: Sum = A XOR B Carry = A AND B Implementation:

Please write comments if you find anything incorrect, or you want to share more information about the topic discussed above

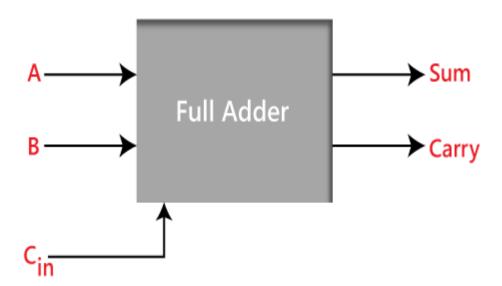

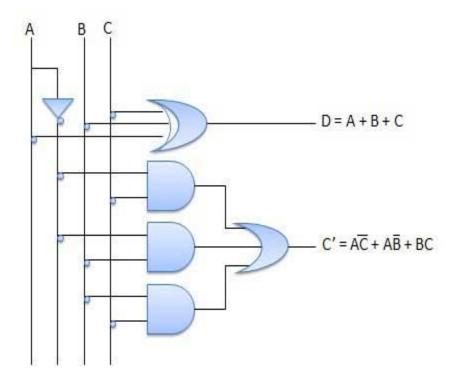

## **Full Adder**

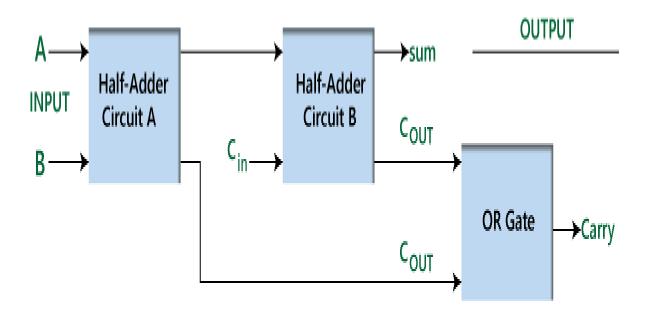

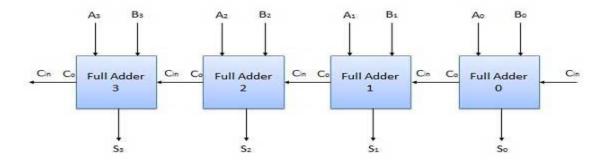

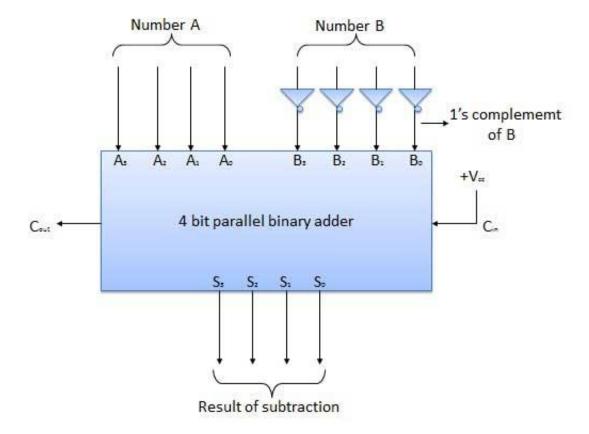

The half adder is used to add only two numbers. To overcome this problem, the full adder was developed. The full adder is used to add three 1-bit binary numbers A, B, and carry C. The full adder has three input states and two output states i.e., sum and carry.

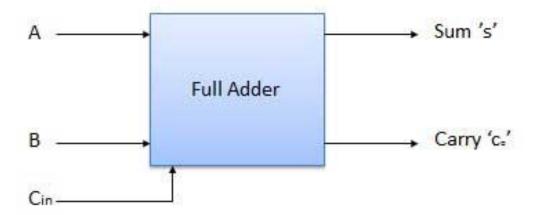

## Block diagram

#### Truth Table

|   | Inputs | Out             | puts |       |

|---|--------|-----------------|------|-------|

| Α | В      | C <sub>in</sub> | Sum  | Carry |

| 0 | 0      | 0               | 0    | 0     |

| 0 | 0      | 1               | 1    | 0     |

| 0 | 1      | 0               | 1    | 0     |

| 0 | 1      | 1               | 0    | 1     |

| 1 | 0      | 0               | 1    | 0     |

| 1 | 0      | 1               | 0    | 1     |

| 1 | 1      | 0               | 0    | 1     |

| 1 | 1      | 1               | 1    | 1     |

In the above table,

- 1. 'A' and' B' are the input variables. These variables represent the two significant bits which are going to be added

- 2. 'C<sub>in</sub>' is the third input which represents the carry. From the previous lower significant position, the carry bit is fetched.

- 3. The 'Sum' and 'Carry' are the output variables that define the output values.

- 4. The eight rows under the input variable designate all possible combinations of 0 and 1 that can occur in these variables.

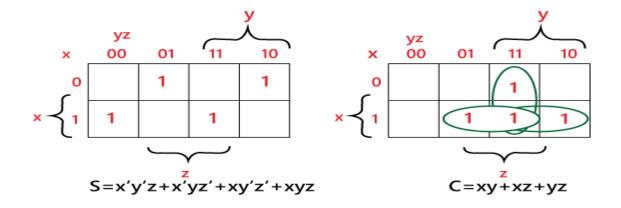

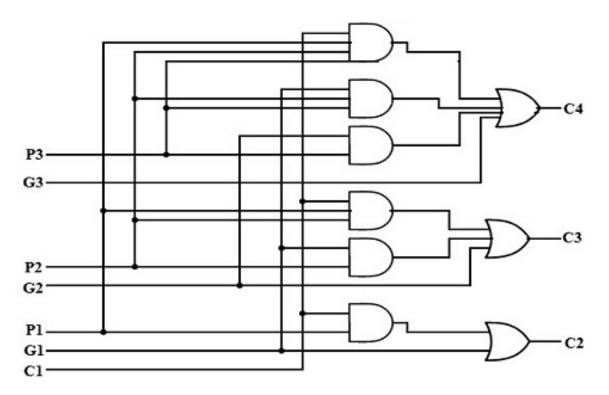

The SOP form can be obtained with the help of K-map as:

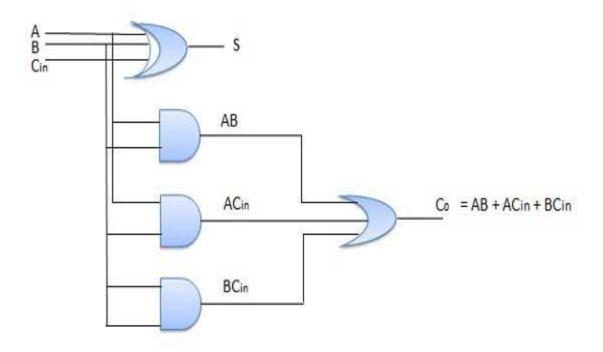

Sum = x' y' z+x' yz+xy' z'+xyzCarry = xy+xz+yz

Construction of Half Adder Circuit:

# Construction of Half Adder Circuit:

The above block diagram describes the construction of the Full adder circuit. In the above circuit, there are two half adder circuits that are combined using the OR gate. The first half adder has two single-bit binary inputs A and B. As we know that, the half adder produces two outputs, i.e., Sum and Carry. The 'Sum' output of the first adder will be the first input of the second half adder, and the 'Carry' output of the first adder will be the second input of the second half adder. The second half adder will again provide 'Sum' and 'Carry'. The final outcome of the Full adder circuit is the 'Sum' bit. In order to find the final output of the 'Carry', we provide the 'Carry' output of the first and the second adder into the OR gate. The outcome of the OR gate will be the final carry out of the full adder circuit.

The MSB is represented by the final 'Carry' bit.

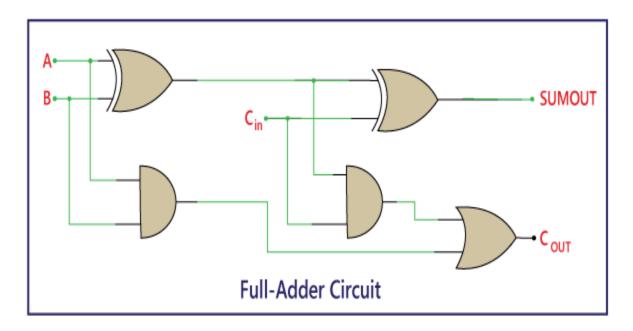

The full adder logic circuit can be constructed using the 'AND' and the 'XOR' gate with an OR gate.

The actual logic circuit of the full adder is shown in the above diagram. The full adder circuit construction can also be represented in a Boolean expression.

#### Sum:

- o Perform the XOR operation of input A and B.

- $_{\circ}$  Perform the XOR operation of the outcome with carry. So, the sum is (A XOR B) XOR  $C_{in}$  which is also represented as: (A  $\oplus$  B)  $\oplus$   $C_{in}$

## Carry:

- 1. Perform the 'AND' operation of input A and B.

- 2. Perform the 'XOR' operation of input A and B.

- Perform the 'OR' operations of both the outputs that come from the previous two steps. So the 'Carry' can be represented as:

A.B + (A ⊕ B)

#### **Subtractor**

**subtractor** An electronic logic circuit for calculating the difference between two binary numbers, the minuend and the number to be subtracted, the subtrahend (see table). A full subtractor performs this calculation with three inputs: minuend bit, subtrahend bit, and borrow bit. It produces two outputs: the difference and the borrow. Full subtractors

thus allow for the inclusion of borrows generated by previous stages of subtraction when forming their output signals, and can be cascaded to form n-bit subtractors. Alternatively the subtract operation can be performed using two half subtractors, which are simpler since they contain only two inputs and produce two outputs.

#### Decoder

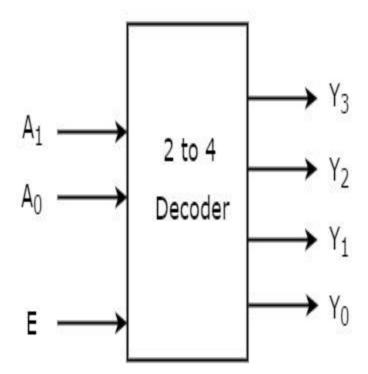

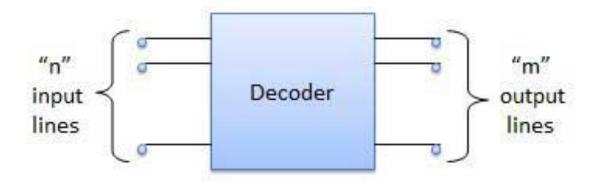

**Decoder** is a combinational circuit that has 'n' input lines and maximum of 2<sup>n</sup> output lines. One of these outputs will be active High based on the combination of inputs present, when the decoder is enabled. That means decoder detects a particular code. The outputs of the decoder are nothing but the **min terms** of 'n' input variables lineslines, when it is enabled.

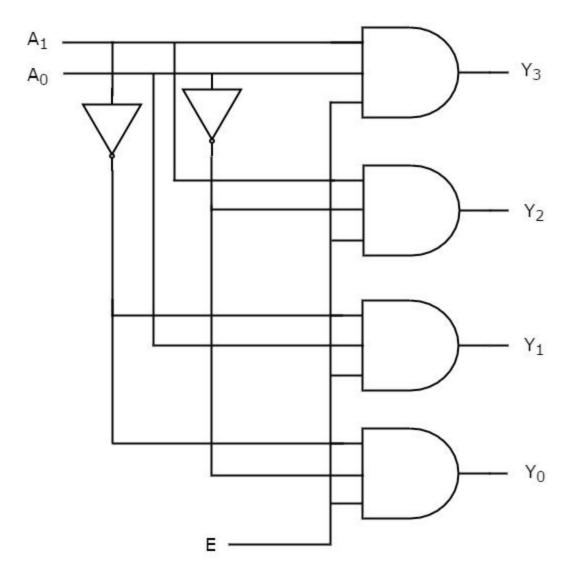

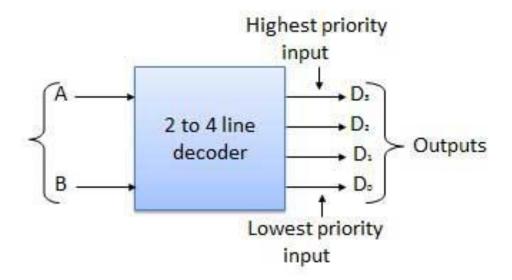

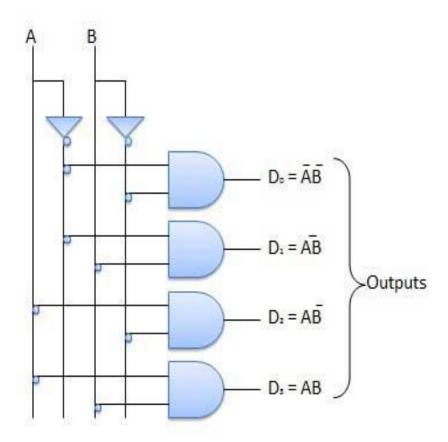

#### 2 to 4 Decoder

Let 2 to 4 Decoder has two inputs  $A_1$  &  $A_0$  and four outputs  $Y_3$ ,  $Y_2$ ,  $Y_1$  &  $Y_0$ . The **block diagram** of 2 to 4 decoder is shown in the following figure.

One of these four outputs will be '1' for each combination of inputs when enable, E is '1'. The **Truth table** of 2 to 4 decoder is shown below.

| Enable | Inp                   | uts            |                       | Out            | outs                  |                |

|--------|-----------------------|----------------|-----------------------|----------------|-----------------------|----------------|

| Е      | <b>A</b> <sub>1</sub> | A <sub>0</sub> | <b>Y</b> <sub>3</sub> | Y <sub>2</sub> | <b>Y</b> <sub>1</sub> | Y <sub>0</sub> |

| 0      | х                     | Х              | 0                     | 0              | 0                     | 0              |

| 1      | 0                     | 0              | 0                     | 0              | 0                     | 1              |

| 1      | 0                     | 1              | 0                     | 0              | 1                     | 0              |

| 1      | 1                     | 0              | 0                     | 1              | 0                     | 0              |

| 1      | 1                     | 1              | 1                     | 0              | 0                     | 0              |

From Truth table, we can write the **Boolean functions** for each output as

Y3=E.A1.A0Y3=E.A1.A0

Y2=E.A1.A0'Y2=E.A1.A0'

Y1=E.A1'.A0Y1=E.A1'.A0

Y0=E.A1'.A0'Y0=E.A1'.A0'

Each output is having one product term. So, there are four product terms in total. We can implement these four product terms by using four AND gates having three inputs each & two inverters. The **circuit diagram** of 2 to 4 decoder is shown in the following figure.

Therefore, the outputs of 2 to 4 decoder are nothing but the **min terms** of two input variables  $A_1$  &  $A_0$ , when enable, E is equal to one. If enable, E is zero, then all the outputs of decoder will be equal to zero.

Similarly, 3 to 8 decoder produces eight min terms of three input variables  $A_2$ ,  $A_1$  &  $A_0$  and 4 to 16 decoder produces sixteen min terms of four input variables  $A_3$ ,  $A_2$ ,  $A_1$  &  $A_0$ .

Implementation of Higher-order Decoders

Now, let us implement the following two higher-order decoders using lower-order decoders.

- 3 to 8 decoder

- 4 to 16 decoder

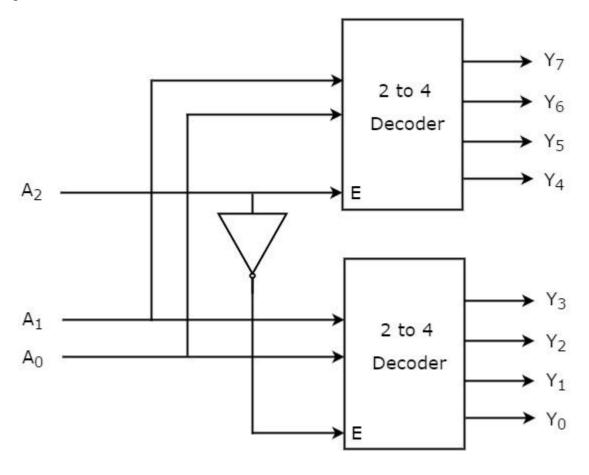

#### 3 to 8 Decoder

In this section, let us implement **3 to 8 decoder using 2 to 4 decoders**. We know that 2 to 4 Decoder has two inputs,  $A_1$  &  $A_0$  and four outputs,  $Y_3$  to  $Y_0$ . Whereas, 3 to 8 Decoder has three inputs  $A_2$ ,  $A_1$  &  $A_0$  and eight outputs,  $Y_7$  to  $Y_0$ .

We can find the number of lower order decoders required for implementing higher order decoder using the following formula.

Requirednumberoflowerorderdecoders=m2m1Requirednumberoflowerorderdecoders=m2m1

## Where,

m1m1 is the number of outputs of lower order decoder.

m2m2 is the number of outputs of higher order decoder.

Here, m1m1 = 4 and m2m2 = 8. Substitute, these two values in the above formula. Requirednumberof2to4decoders=84=2Requirednumberof2to4decoders=84=2

Therefore, we require two 2 to 4 decoders for implementing one 3 to 8 decoder. The **block diagram** of 3 to 8 decoder using 2 to 4 decoders is shown in the following figure.

The parallel inputs  $A_1$  &  $A_0$  are applied to each 2 to 4 decoder. The complement of input  $A_2$  is connected to Enable, E of lower 2 to 4 decoder in order to get the outputs,  $Y_3$  to  $Y_0$ . These are the **lower four min terms**. The input,  $A_2$  is directly connected to Enable, E of upper 2 to 4 decoder in order to get the outputs,  $Y_7$  to  $Y_4$ . These are the **higher four min terms**.

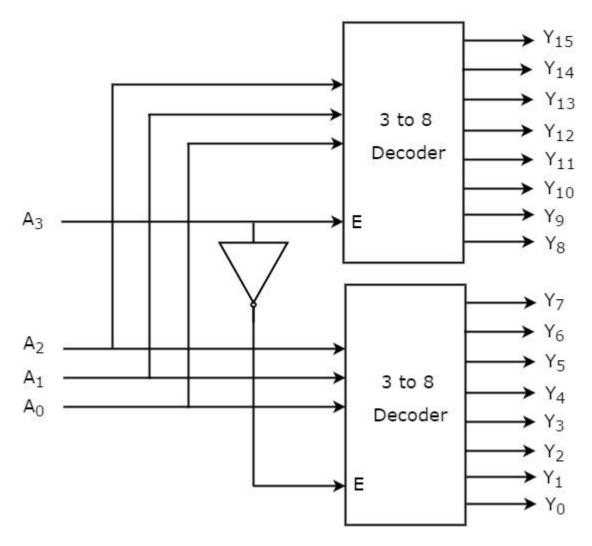

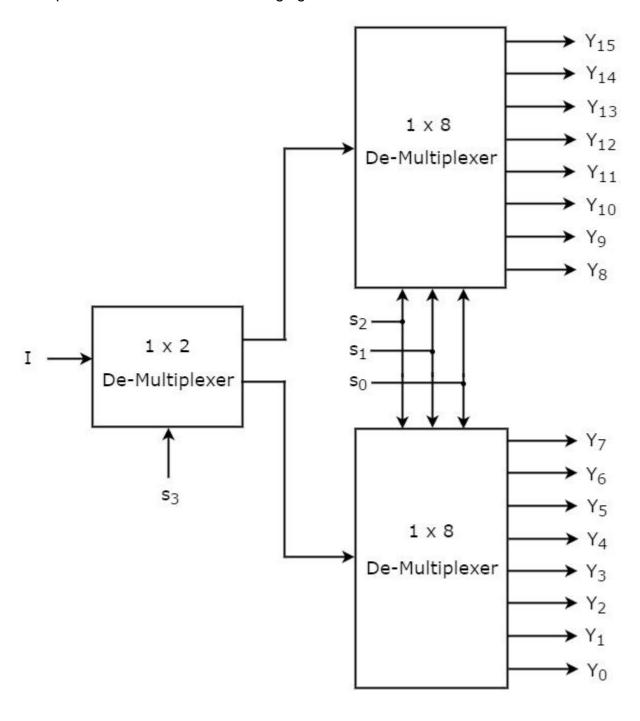

#### 4 to 16 Decoder

In this section, let us implement **4 to 16 decoder using 3 to 8 decoders**. We know that 3 to 8 Decoder has three inputs  $A_2$ ,  $A_1$  &  $A_0$  and eight outputs,  $Y_7$  to  $Y_0$ . Whereas, 4 to 16 Decoder has four inputs  $A_3$ ,  $A_2$ ,  $A_1$  &  $A_0$  and sixteen outputs,  $Y_{15}$  to  $Y_0$

We know the following formula for finding the number of lower order decoders required.

Requirednumberoflowerorderdecoders=m2m1Requirednumberoflowerorderdecoders=m2m1

Substitute, m1m1 = 8 and m2m2 = 16 in the above formula.

Requirednumberof3to8decoders=168=2Requirednumberof3to8decoders=168=2

Therefore, we require two 3 to 8 decoders for implementing one 4 to 16 decoder. The **block diagram** of 4 to 16 decoder using 3 to 8 decoders is shown in the following figure.

## **Encoders**

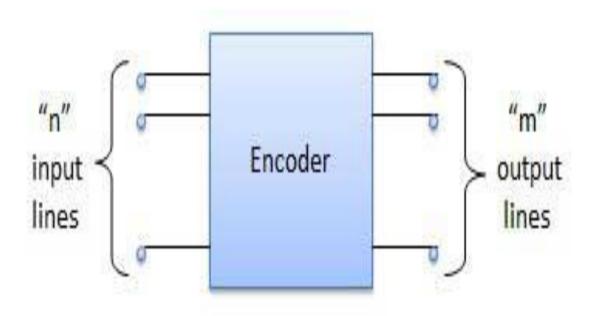

An **Encoder** is a combinational circuit that performs the reverse operation of Decoder. It has maximum of 2<sup>n</sup> input lines and 'n' output lines. It will produce a binary code equivalent to the input, which is active High. Therefore, the encoder encodes 2<sup>n</sup> input lines with 'n' bits. It is optional to represent the enable signal in encoders.

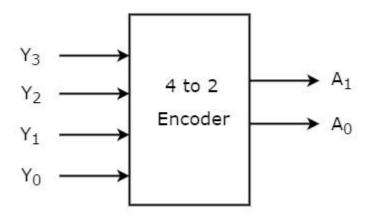

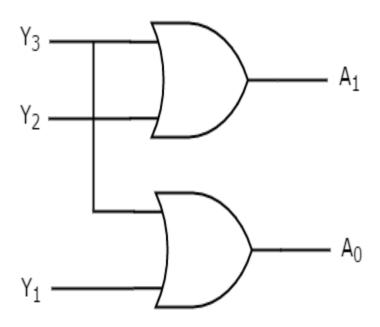

#### 4 to 2 Encoder

Let 4 to 2 Encoder has four inputs  $Y_3$ ,  $Y_2$ ,  $Y_1$  &  $Y_0$  and two outputs  $A_1$  &  $A_0$ . The **block diagram** of 4 to 2 Encoder is shown in the following figure.

At any time, only one of these 4 inputs can be '1' in order to get the respective binary code at the output. The **Truth table** of 4 to 2 encoder is shown below.

|                       | Inp            | Out                   | puts           |                       |                |

|-----------------------|----------------|-----------------------|----------------|-----------------------|----------------|

| <b>Y</b> <sub>3</sub> | Y <sub>2</sub> | <b>Y</b> <sub>1</sub> | Y <sub>0</sub> | <b>A</b> <sub>1</sub> | A <sub>0</sub> |

| 0                     | 0              | 0                     | 1              | 0                     | 0              |

| 0                     | 0              | 1                     | 0              | 0                     | 1              |

| 0                     | 1              | 0                     | 0              | 1                     | 0              |

| 1                     | 0              | 0                     | 0              | 1                     | 1              |

From Truth table, we can write the **Boolean functions** for each output as

We can implement the above two Boolean functions by using two input OR gates. The **circuit diagram** of 4 to 2 encoder is shown in the following figure.

The above circuit diagram contains two OR gates. These OR gates encode the four inputs with two bits

## Octal to Binary Encoder

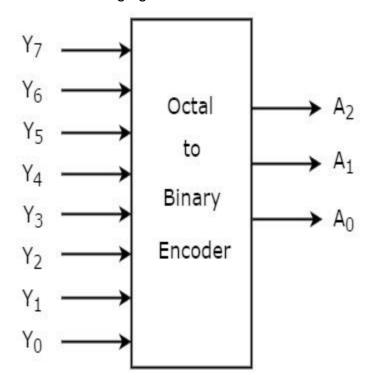

Octal to binary Encoder has eight inputs,  $Y_7$  to  $Y_0$  and three outputs  $A_2$ ,  $A_1$  &  $A_0$ . Octal to binary encoder is nothing but 8 to 3 encoder. The **block diagram** of octal to binary Encoder is shown in the following figure.

At any time, only one of these eight inputs can be '1' in order to get the respective binary code. The **Truth table** of octal to binary encoder is shown below.

|                       | Inputs                |                       |                       |                       |                |                       |                |                | Outputs               |       |

|-----------------------|-----------------------|-----------------------|-----------------------|-----------------------|----------------|-----------------------|----------------|----------------|-----------------------|-------|

| <b>Y</b> <sub>7</sub> | <b>Y</b> <sub>6</sub> | <b>Y</b> <sub>5</sub> | <b>Y</b> <sub>4</sub> | <b>Y</b> <sub>3</sub> | Y <sub>2</sub> | <b>Y</b> <sub>1</sub> | Y <sub>0</sub> | A <sub>2</sub> | <b>A</b> <sub>1</sub> | $A_0$ |

| 0                     | 0                     | 0                     | 0                     | 0                     | 0              | 0                     | 1              | 0              | 0                     | 0     |

| 0                     | 0                     | 0                     | 0                     | 0                     | 0              | 1                     | 0              | 0              | 0                     | 1     |

| 0 | 0 | 0 | 0 | 0 | 1 | 0 | 0 | 0 | 1 | 0 |

|---|---|---|---|---|---|---|---|---|---|---|

| 0 | 0 | 0 | 0 | 1 | 0 | 0 | 0 | 0 | 1 | 1 |

| 0 | 0 | 0 | 1 | 0 | 0 | 0 | 0 | 1 | 0 | 0 |

| 0 | 0 | 1 | 0 | 0 | 0 | 0 | 0 | 1 | 0 | 1 |

| 0 | 1 | 0 | 0 | 0 | 0 | 0 | 0 | 1 | 1 | 0 |

| 1 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 1 | 1 | 1 |

From Truth table, we can write the **Boolean functions** for each output as

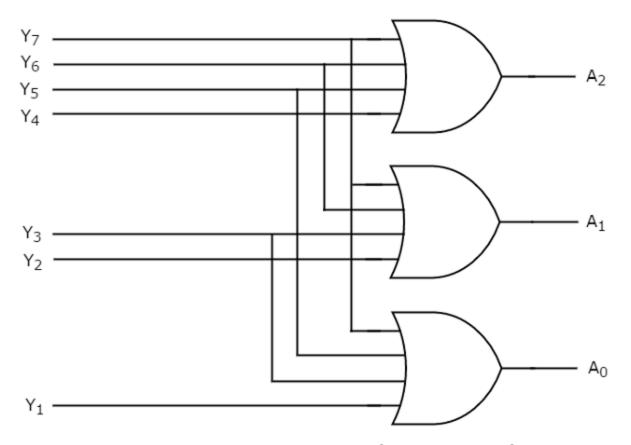

We can implement the above Boolean functions by using four input OR gates. The **circuit diagram** of octal to binary encoder is shown in the following figure.

The above circuit diagram contains three 4-input OR gates. These OR gates encode the eight inputs with three bits.

#### Drawbacks of Encoder

Following are the drawbacks of normal encoder.

- There is an ambiguity, when all outputs of encoder are equal to zero. Because, it could be the code corresponding to the inputs, when only least significant input is one or when all inputs are zero.

- If more than one input is active High, then the encoder produces an output, which may not be the correct code. For **example**, if both Y<sub>3</sub> and Y<sub>6</sub> are '1', then the encoder produces 111 at the output. This is neither equivalent code corresponding to Y<sub>3</sub>, when it is '1' nor the equivalent code corresponding to Y<sub>6</sub>, when it is '1'.

So, to overcome these difficulties, we should assign priorities to each input of encoder. Then, the output of encoder will be the binarybinary code corresponding to the active High inputss, which has higher priority. This encoder is called as **priority encoder**.

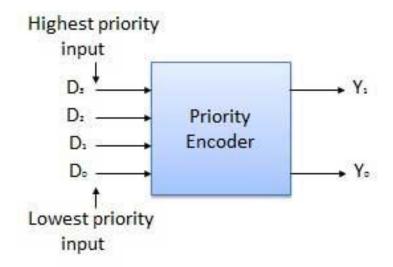

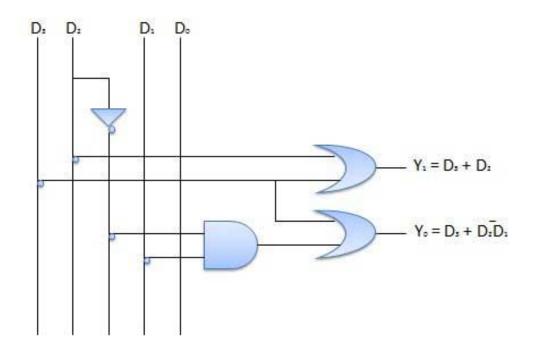

## **Priority Encoder**

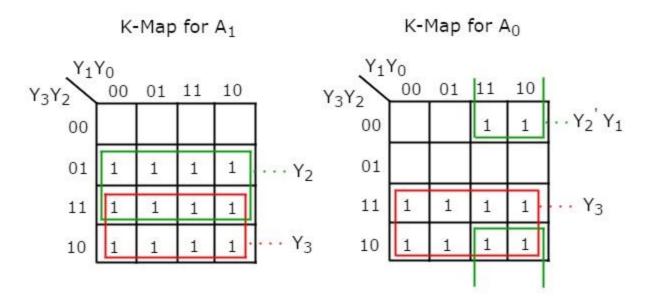

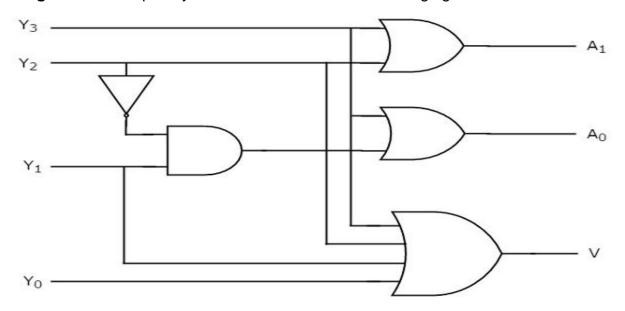

A 4 to 2 priority encoder has four inputs  $Y_3$ ,  $Y_2$ ,  $Y_1$  &  $Y_0$  and two outputs  $A_1$  &  $A_0$ . Here, the input,  $Y_3$  has the highest priority, whereas the input,  $Y_0$  has the lowest priority. In this case, even if more than one input is '1' at the same time, the output will be the binarybinary code corresponding to the input, which is having **higher priority**.

We considered one more **output**, **V** in order to know, whether the code available at outputs is valid or not.

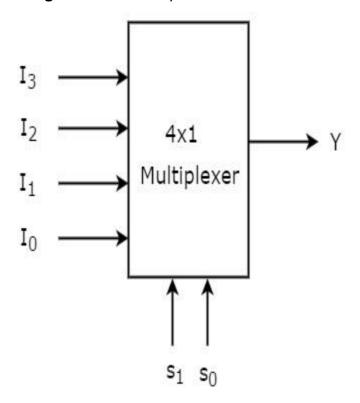

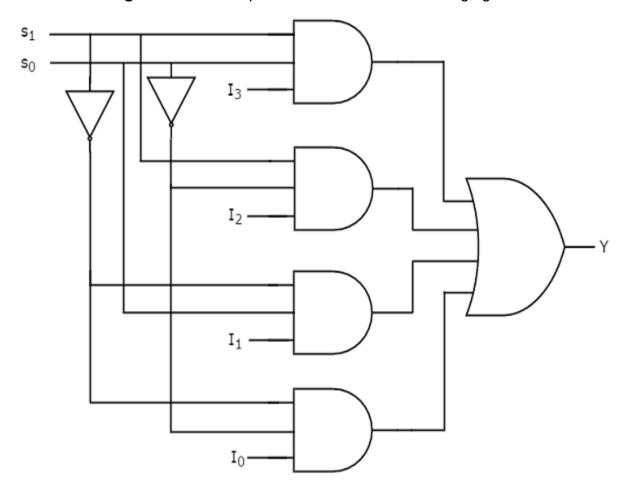

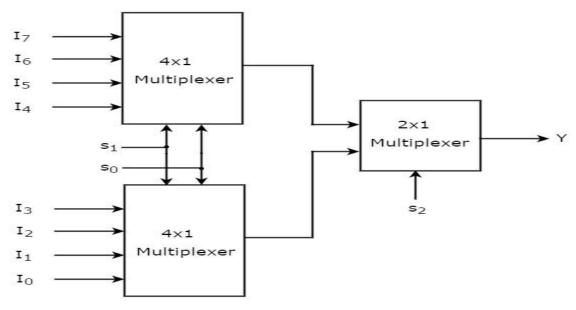

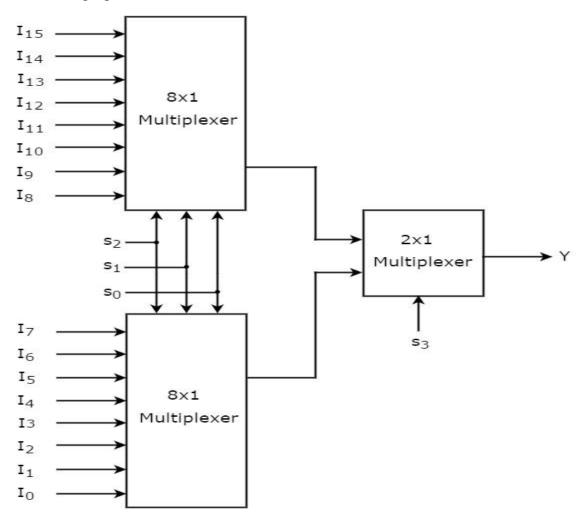

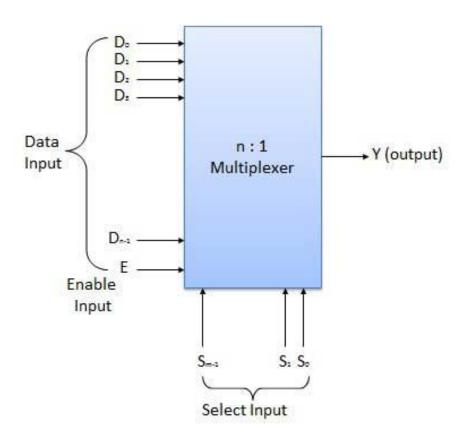

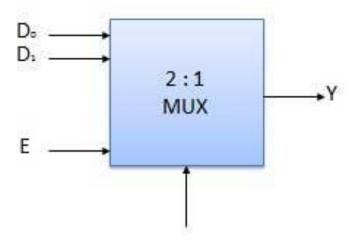

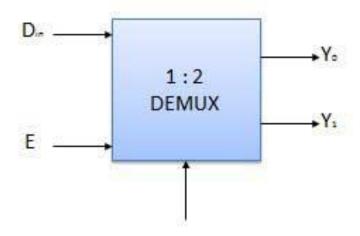

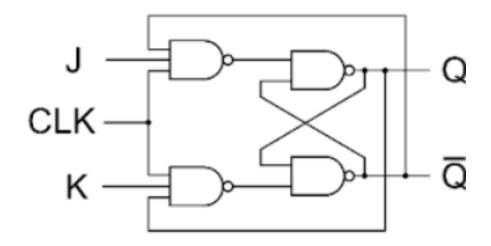

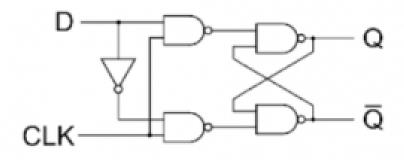

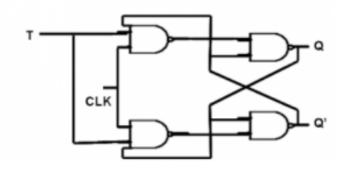

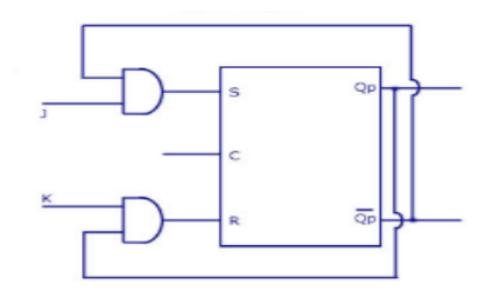

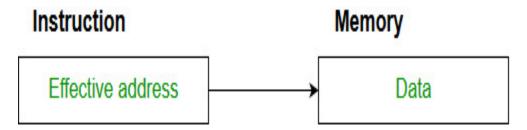

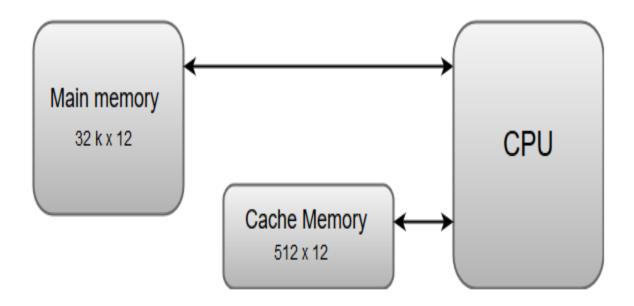

- If at least one input of the encoder is '1', then the code available at outputs is a valid one. In this case, the output, V will be equal to 1.